# Programmable Logic Data Book 1994/1995

#### How To Use This Book

#### **Overall Organization**

This book has been organized by product type, beginning with Product Information. The products are next, starting with Small PLDs, then CPLDs, FPGAs, and Software. A section containing Quality and Reliability is next, followed by a Package Diagrams section. Within each section, data sheets are arranged in order of part number.

#### **Recommended Search Paths**

To search by: Use:

Product line Table of Contents or flip

through the book using the tabs on the right-hand pages.

Size The Product Selector Guide

in section 1.

Numeric part number Numeric Device Index. The

book is also arranged in order of part number.

Other manufacturer's The Cross Reference Guide

part number in section 1.

Military part number The Military Selector Guide

in section 1.

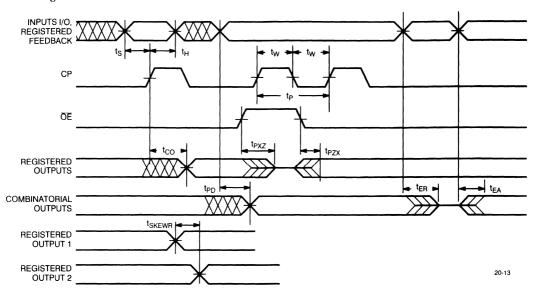

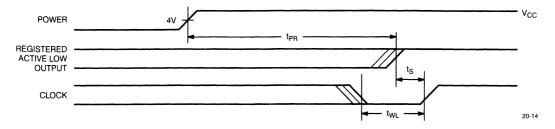

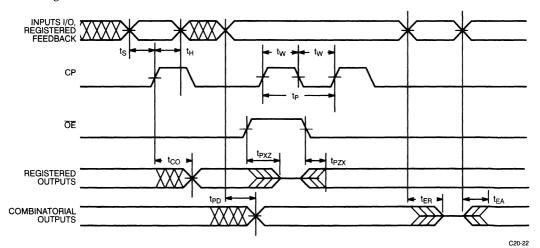

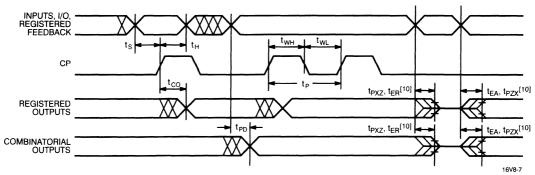

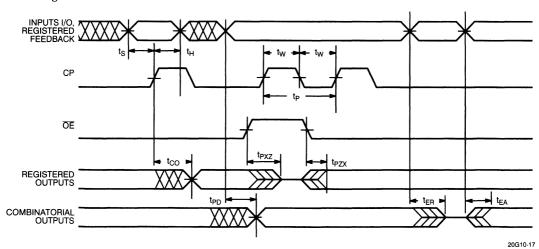

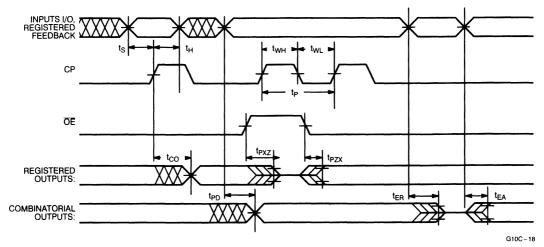

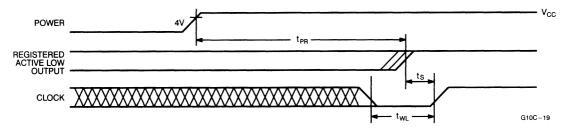

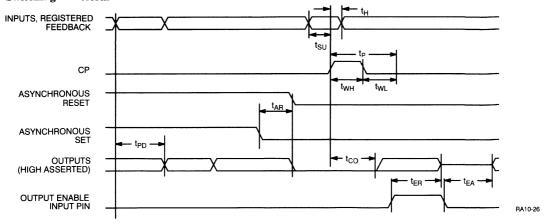

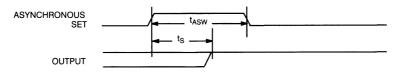

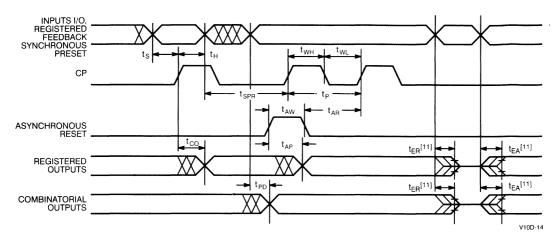

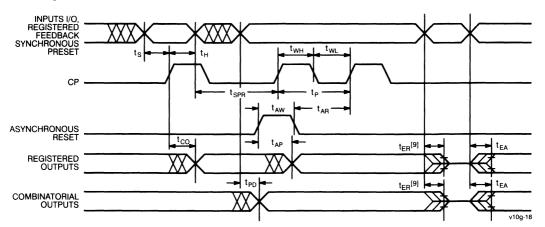

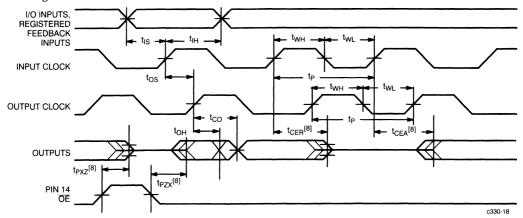

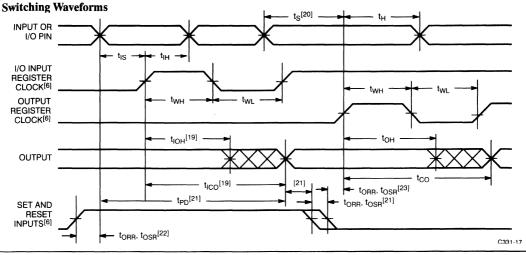

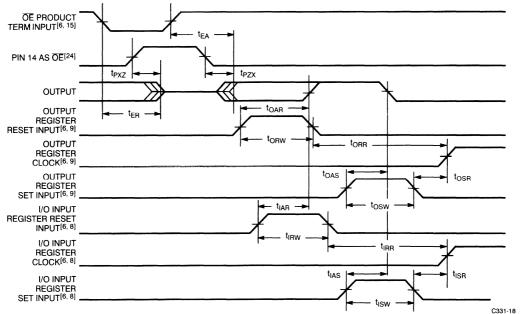

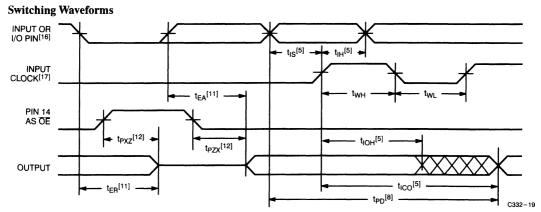

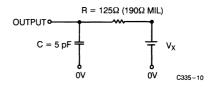

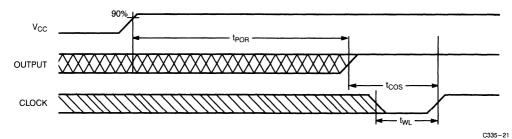

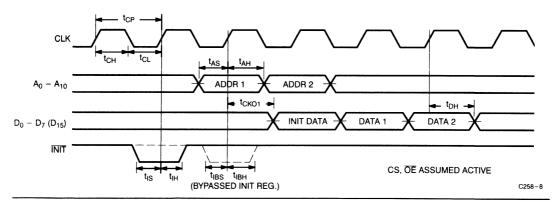

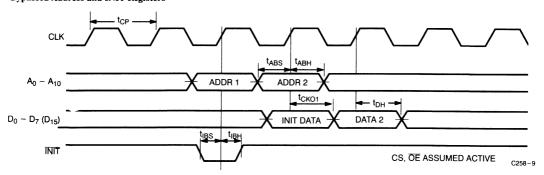

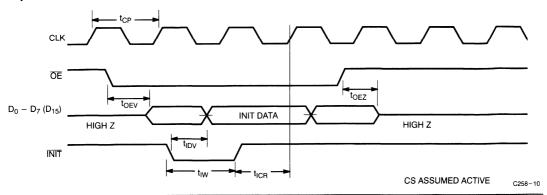

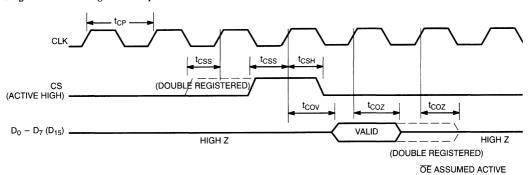

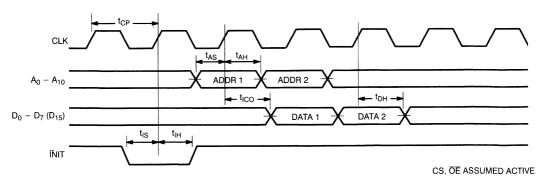

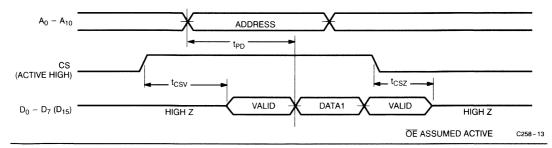

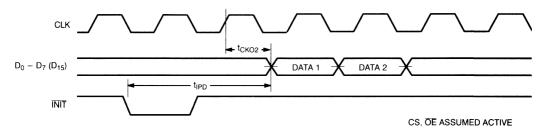

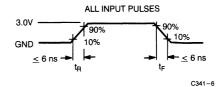

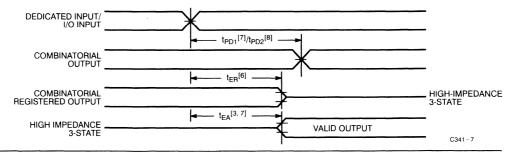

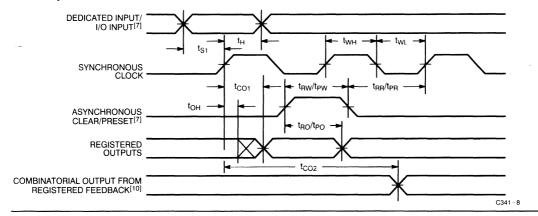

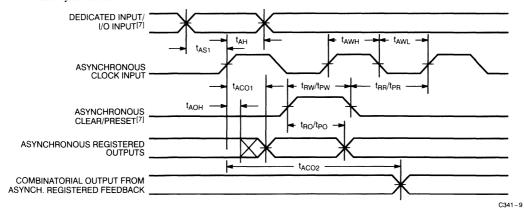

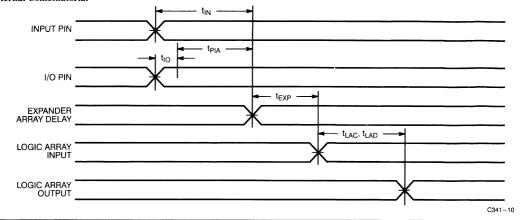

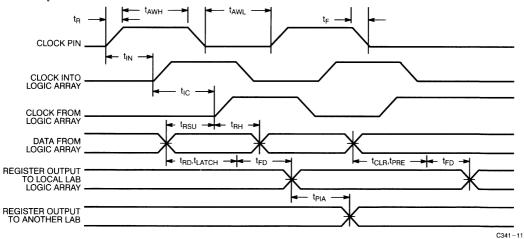

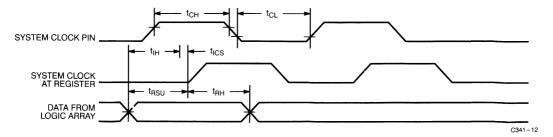

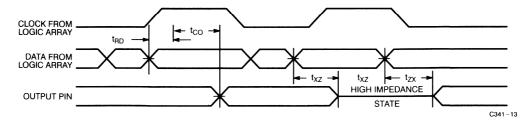

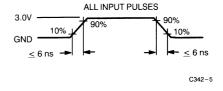

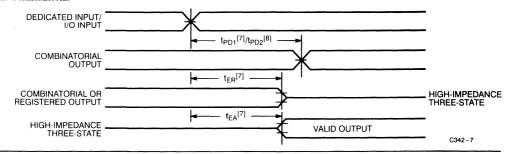

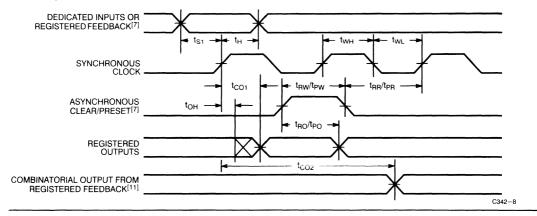

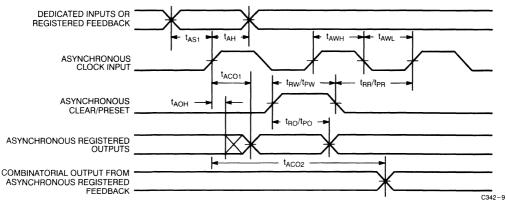

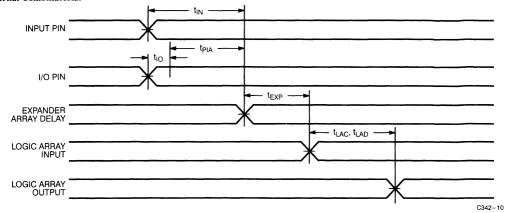

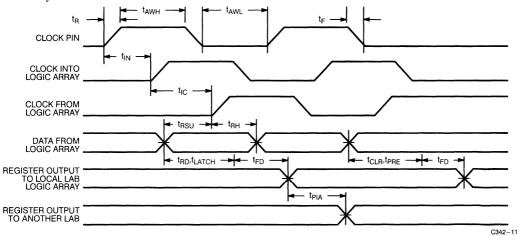

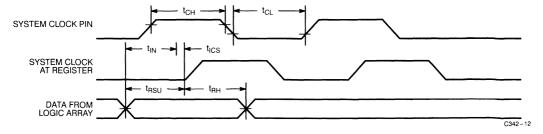

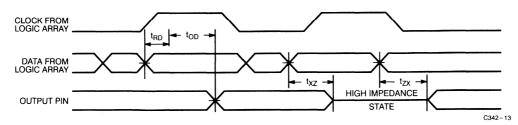

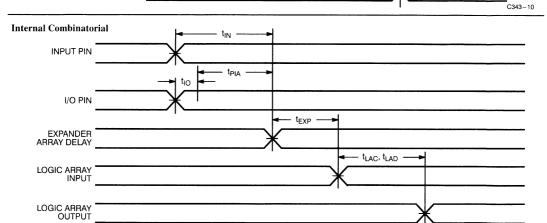

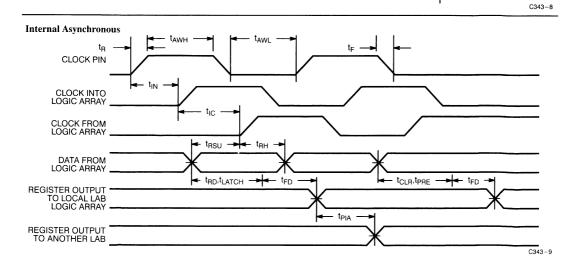

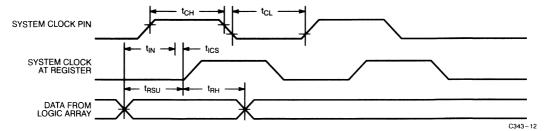

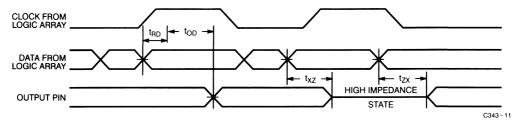

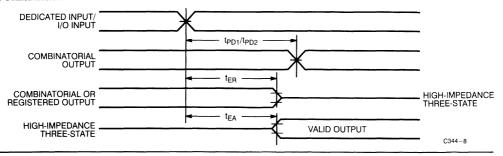

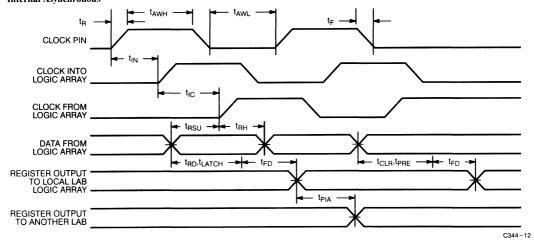

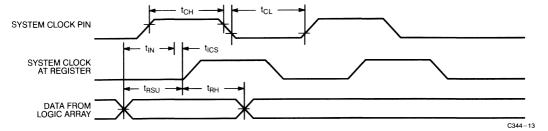

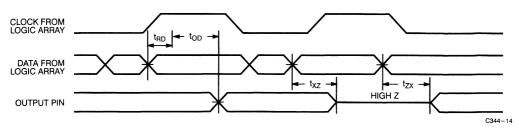

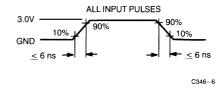

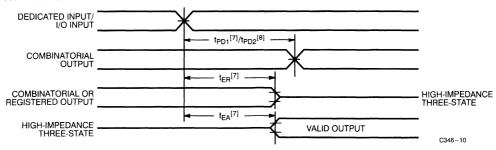

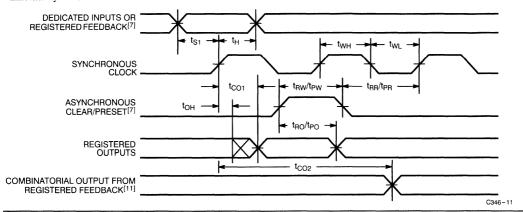

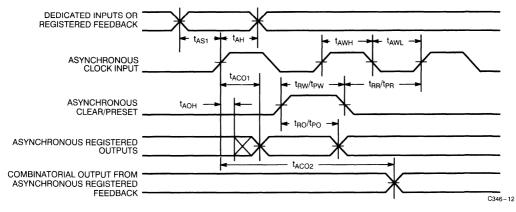

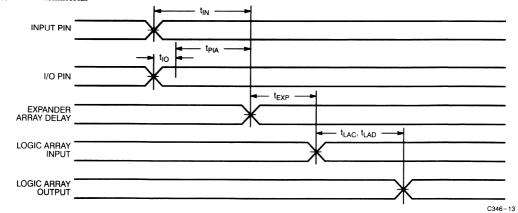

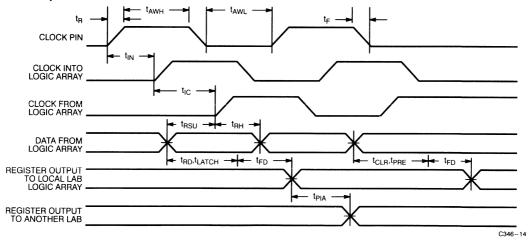

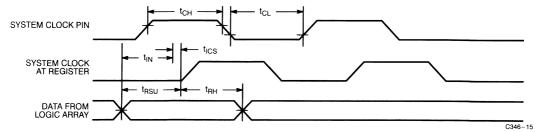

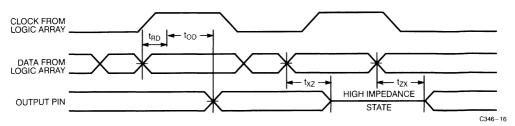

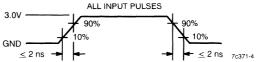

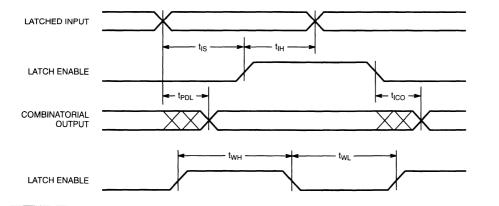

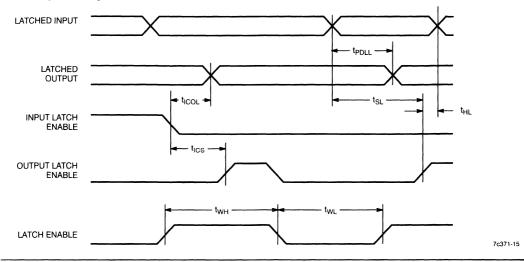

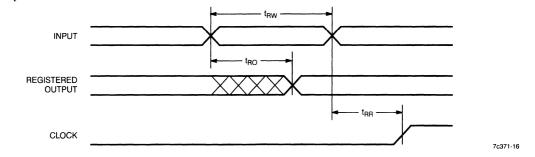

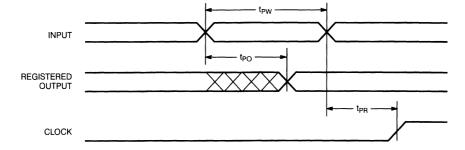

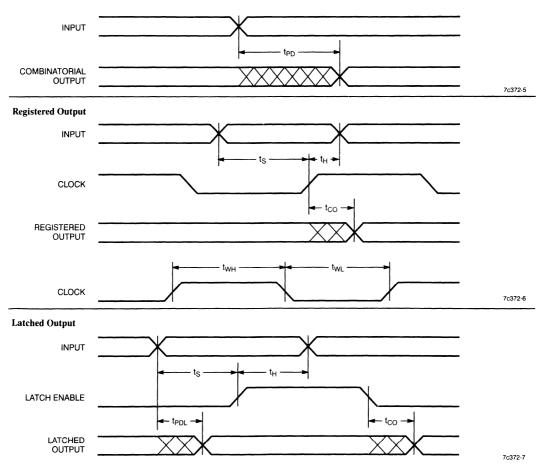

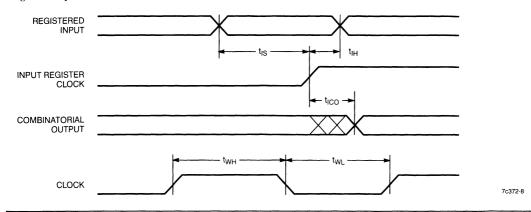

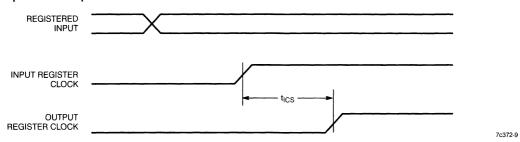

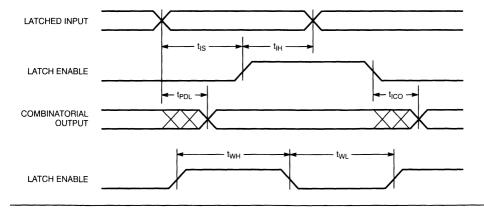

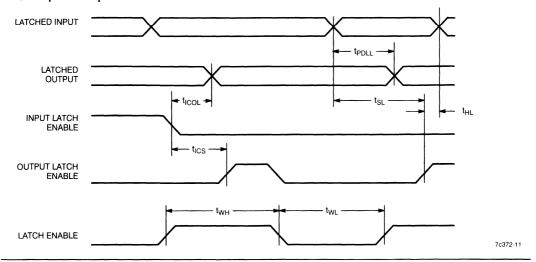

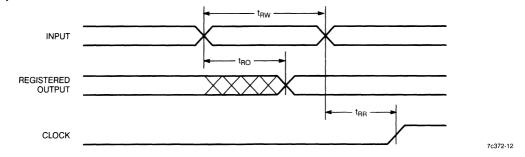

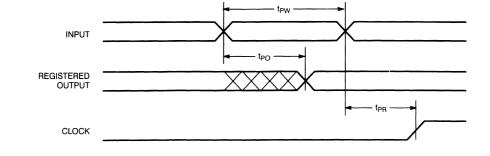

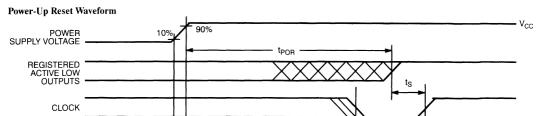

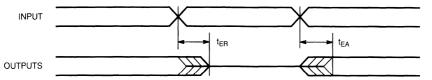

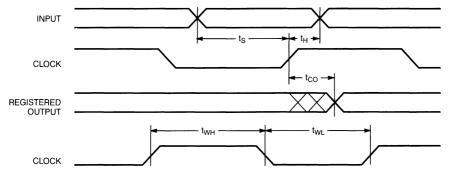

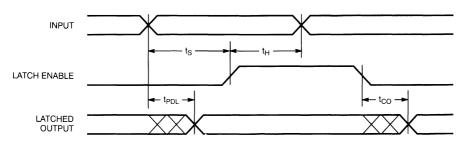

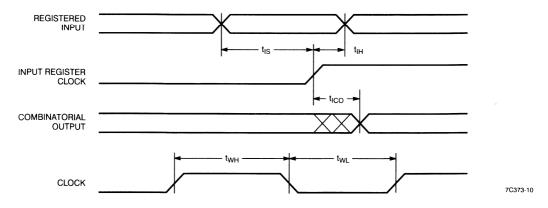

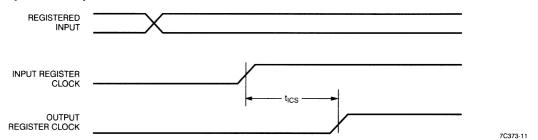

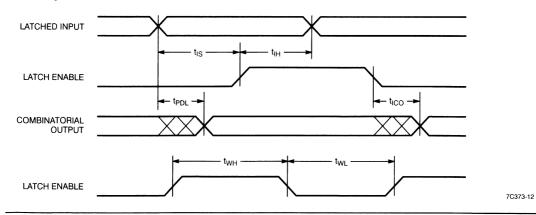

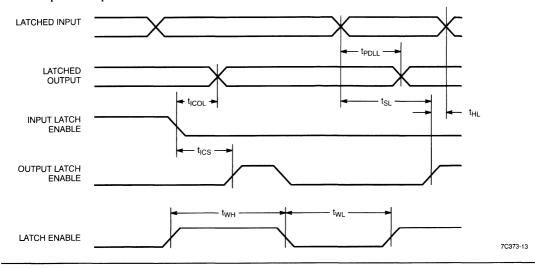

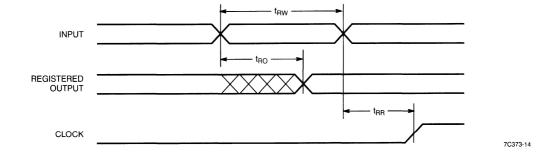

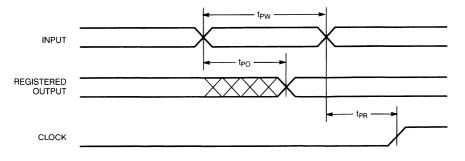

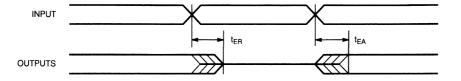

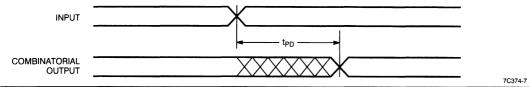

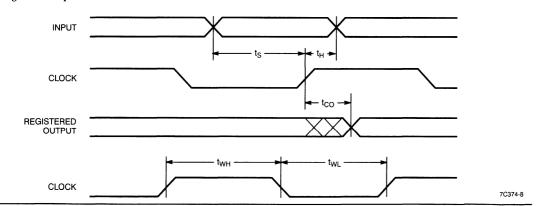

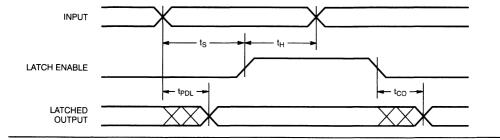

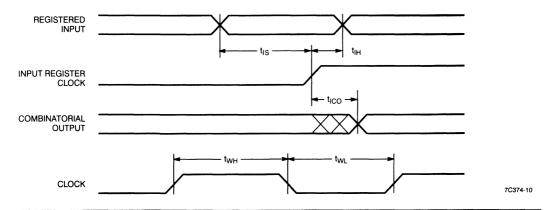

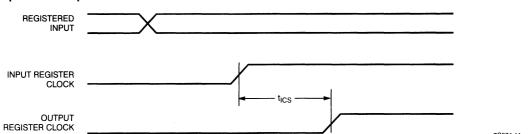

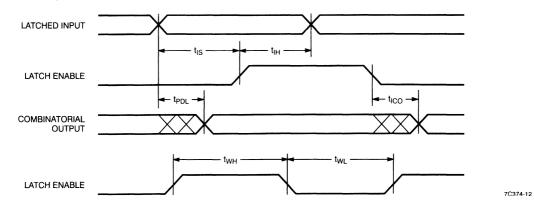

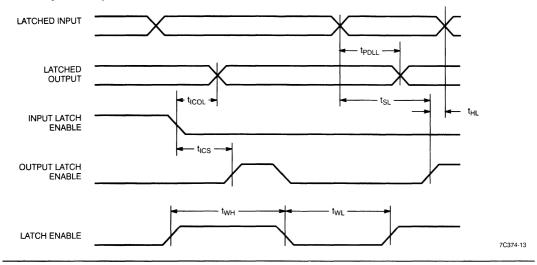

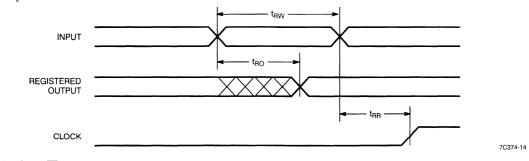

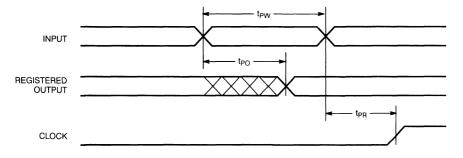

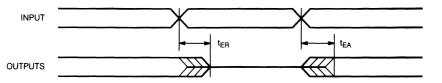

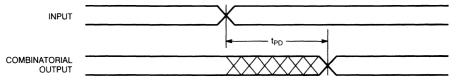

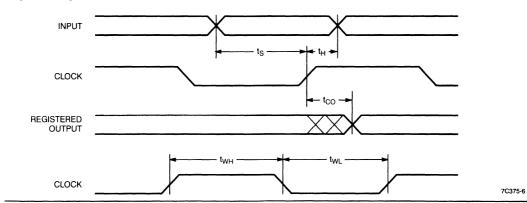

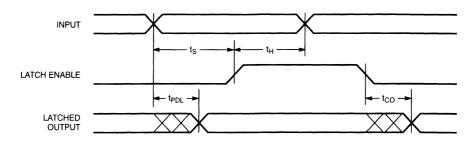

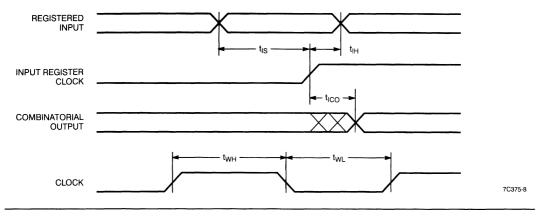

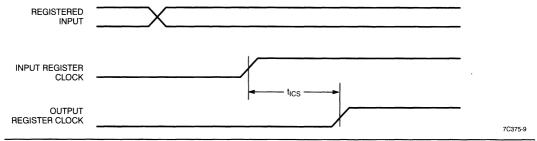

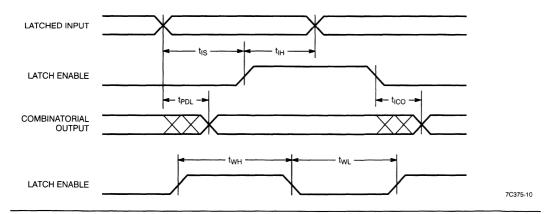

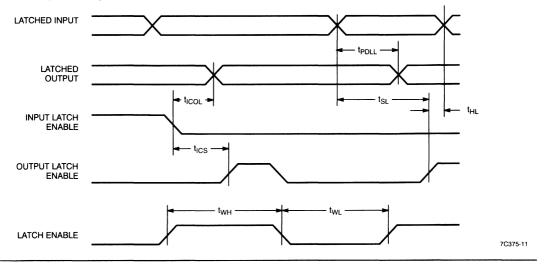

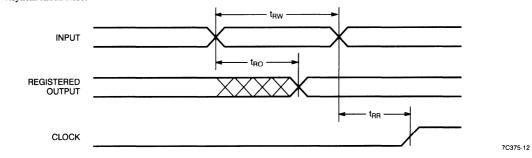

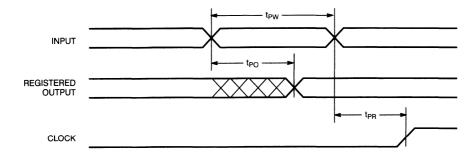

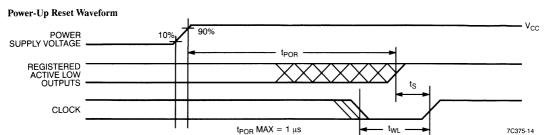

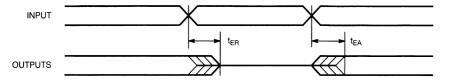

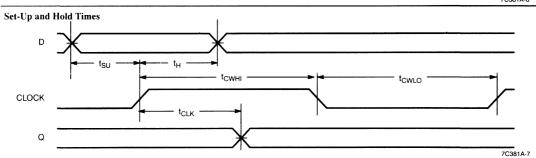

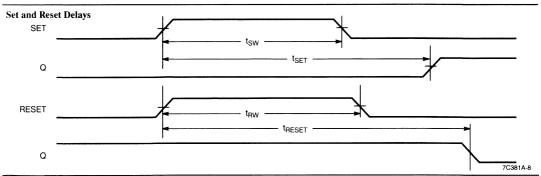

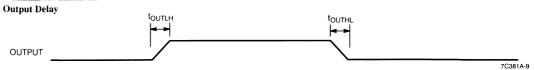

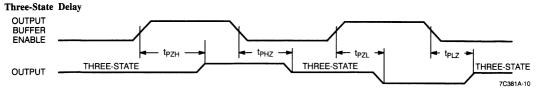

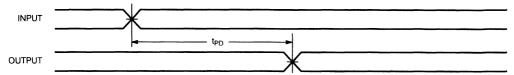

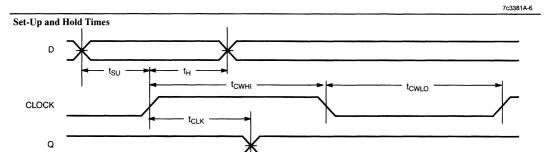

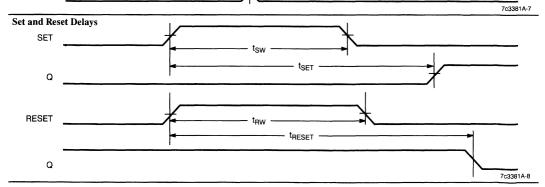

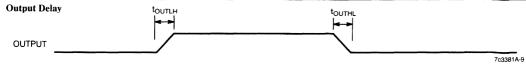

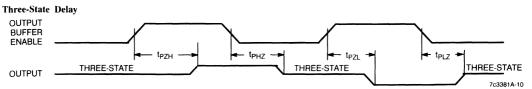

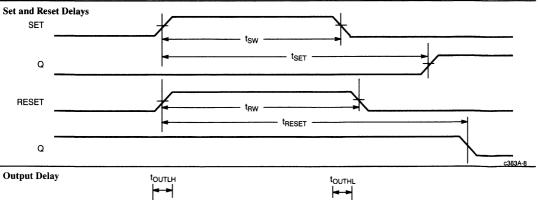

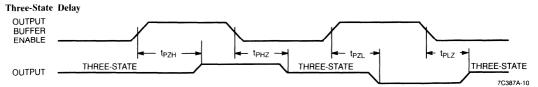

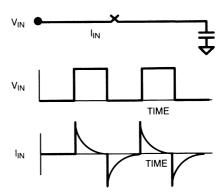

#### **Key to Waveform Diagrams**

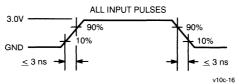

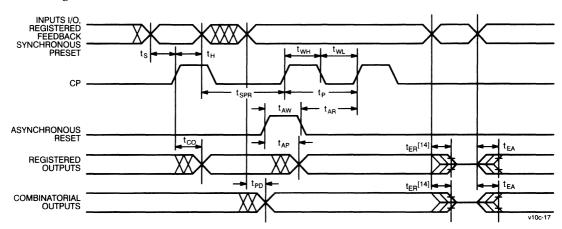

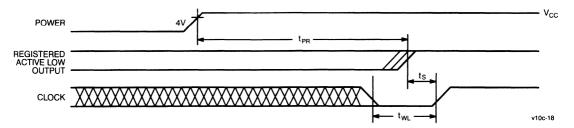

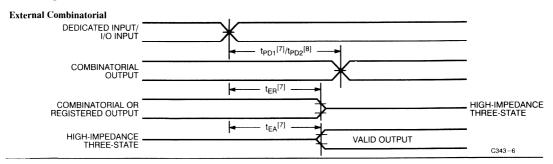

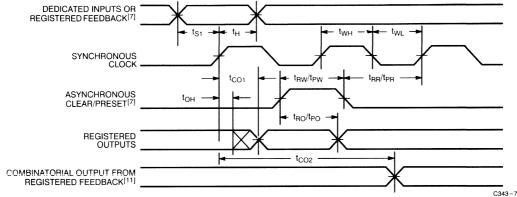

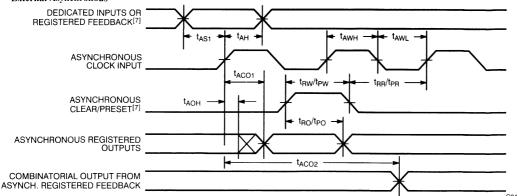

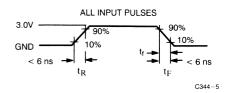

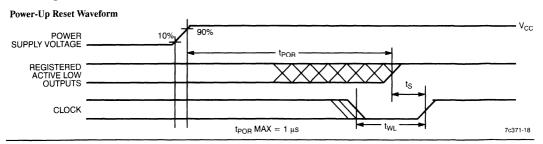

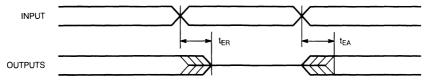

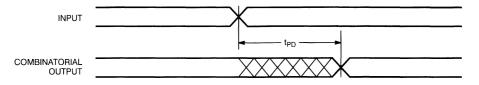

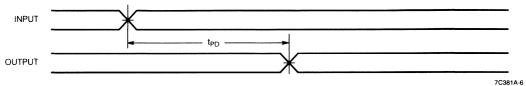

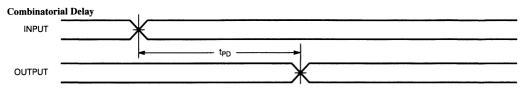

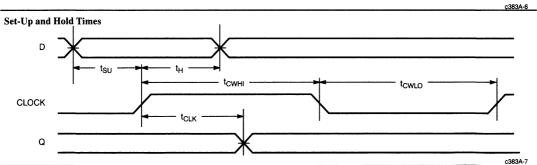

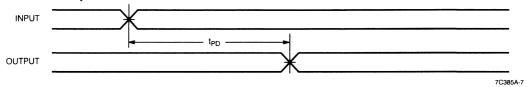

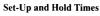

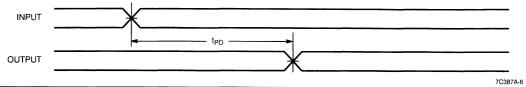

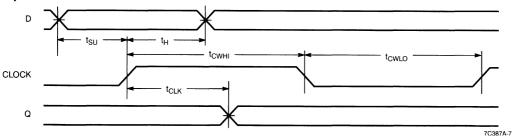

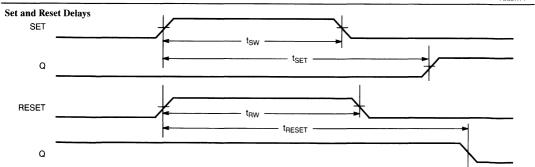

= Rising edge of signal will occur during this time.

= Falling edge of signal will occur during this time.

Signal may transition during this time (don't care condition).

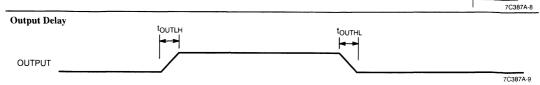

Signal changes from highimpedance state to valid logic level during this time.

Signal changes from valid logic level to high-impedance state during this time.

#### Published July 7, 1994

All trademarks listed herein are of their respective companies.

<sup>©</sup> Cypress Semiconductor Corporation, 1994. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.

| Table of Contents          | Page Numbe                                            |

|----------------------------|-------------------------------------------------------|

| General Product Infor      | mation                                                |

| Cypress Semiconductor Ba   | ckground 1-                                           |

|                            |                                                       |

|                            | letin Board System (BBS) Announcement 1-              |

|                            |                                                       |

|                            |                                                       |

| Product Line Cross Referen | nce                                                   |

|                            | 1-1                                                   |

|                            | uide                                                  |

|                            | ion 1–1                                               |

| Small PLDs (Program        | mable Logic Devices)                                  |

| Introduction to Cypress PL | Ds 2-                                                 |

| Device                     | Description                                           |

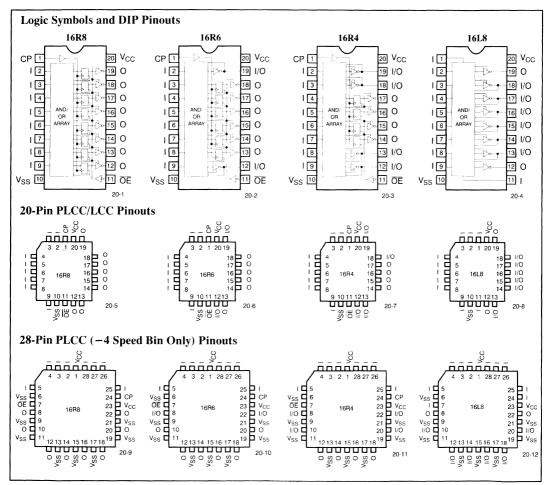

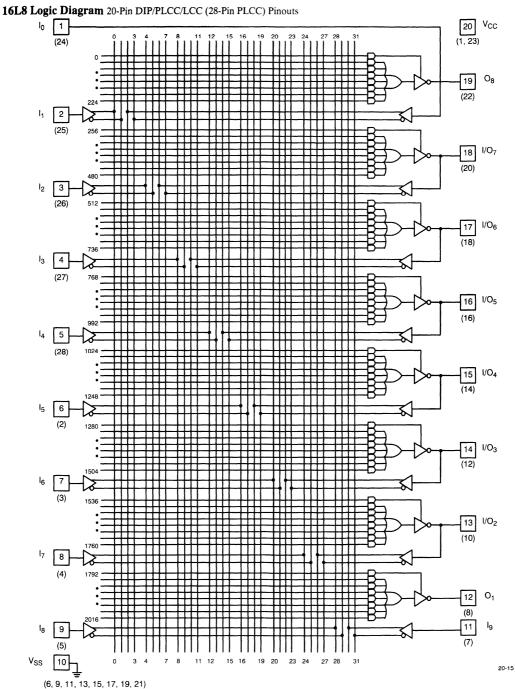

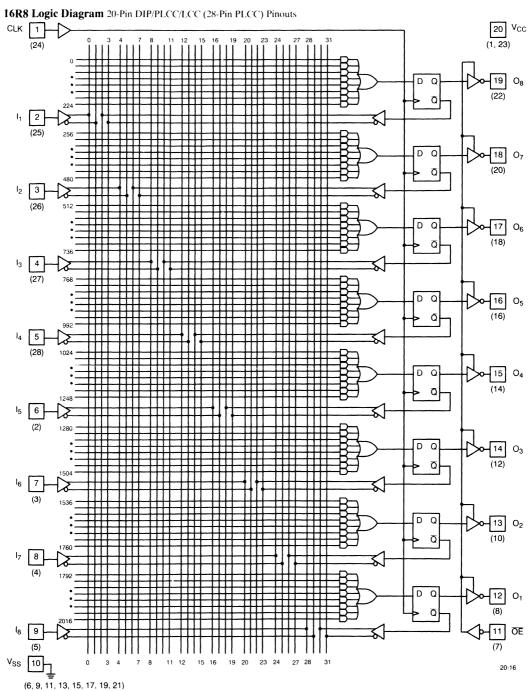

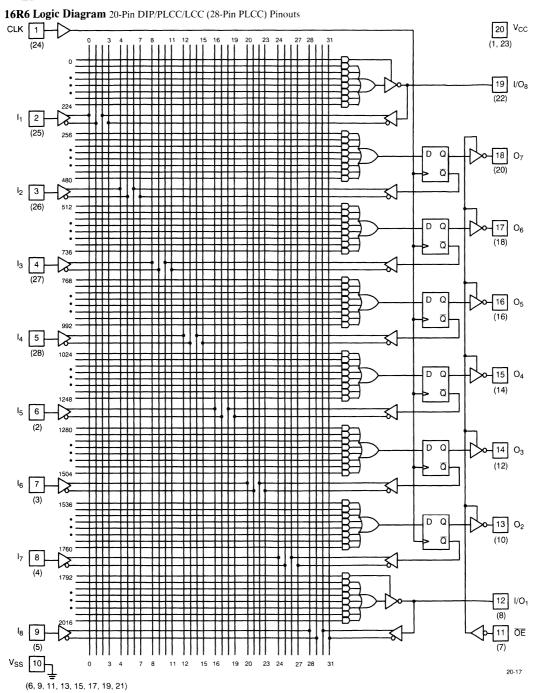

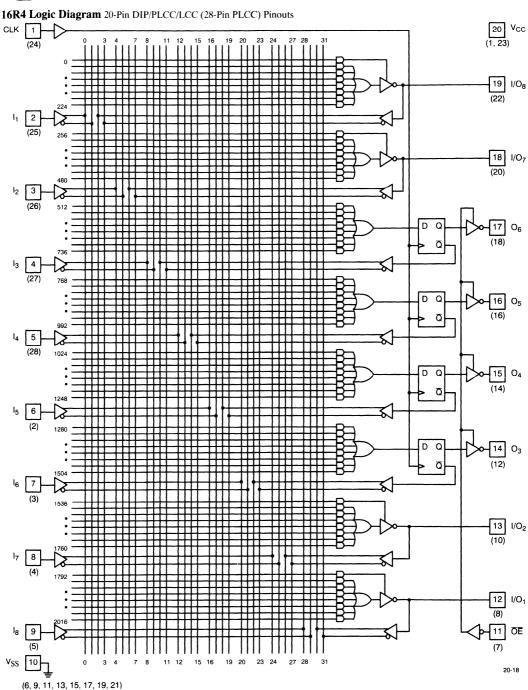

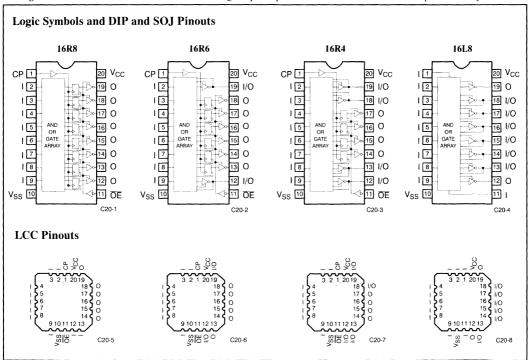

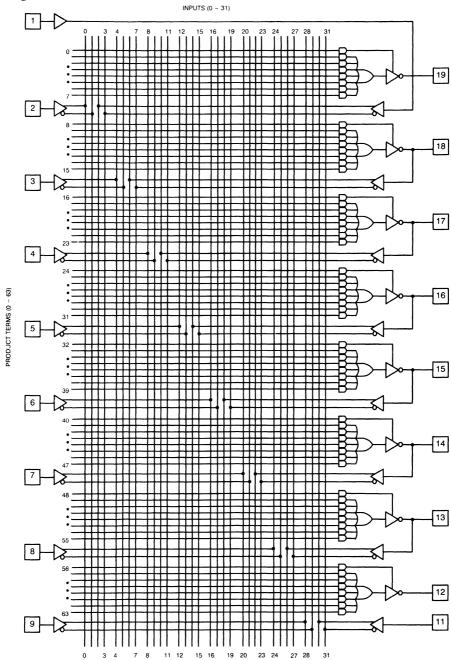

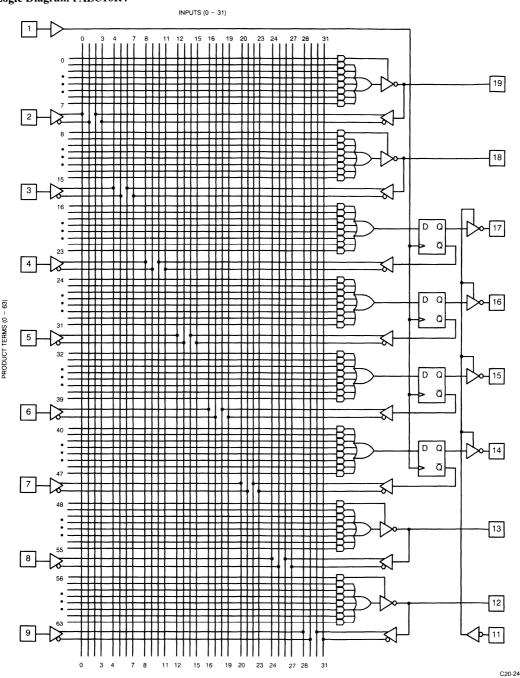

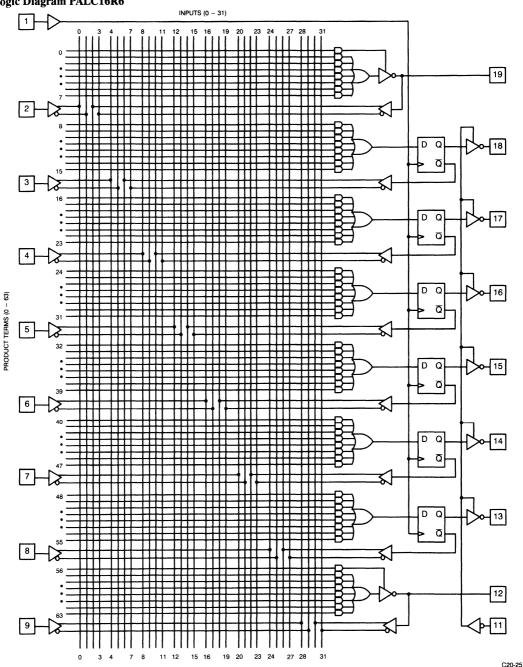

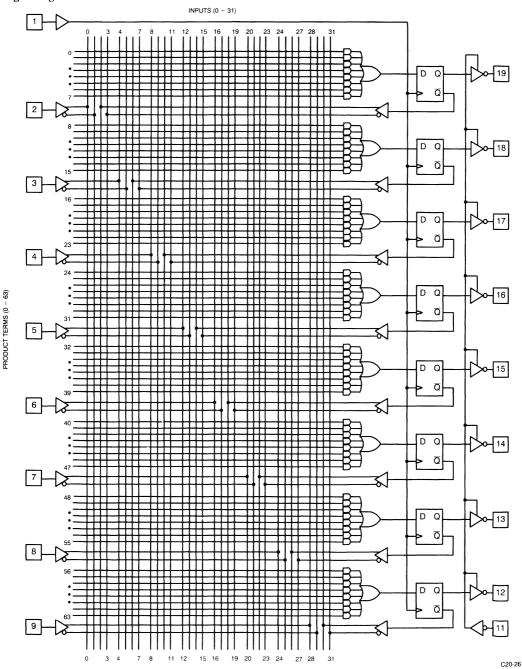

| PAL20 Series               | 4.5-ns, Industry-Standard PLDs 16L8, 16R8, 16R6, 16R4 |

| PALC20 Series              | Reprogrammable CMOS PALC 16L8, 16R8, 16R6, 16R4       |

| PALCE16V8                  | Flash Erasable, Reprogrammable CMOS PAL Device        |

| PALCE20V8                  | Flash Erasable, Reprogrammable CMOS PAL Device        |

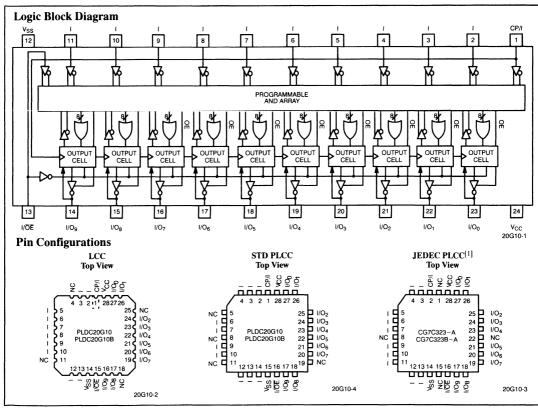

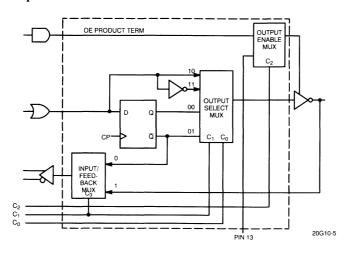

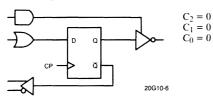

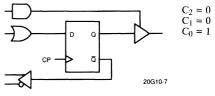

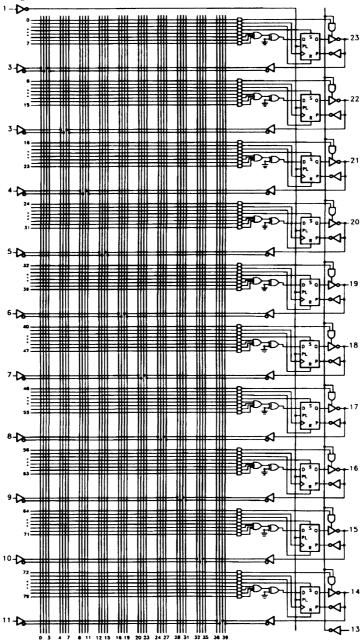

| PLDC20G10                  | CMOS Generic 24-Pin Reprogrammable Logic Device       |

| PLDC20G10B                 | CMOS Generic 24-Pin Reprogrammable Logic Device       |

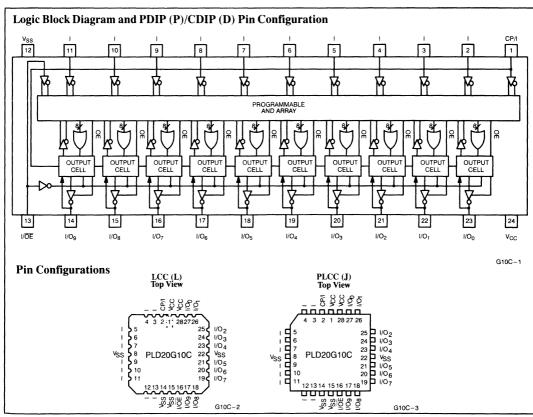

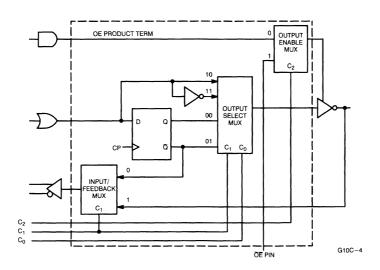

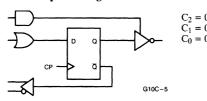

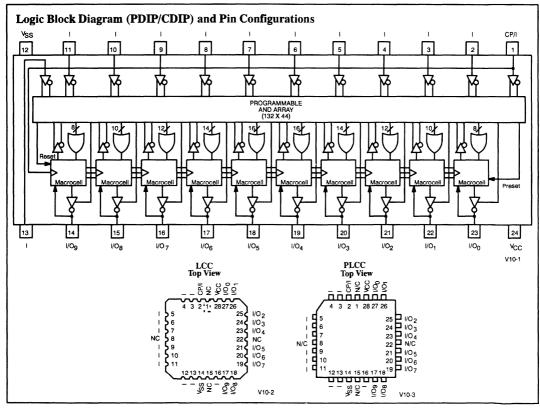

| PLD20G10C                  | Generic 24-Pin PAL Device                             |

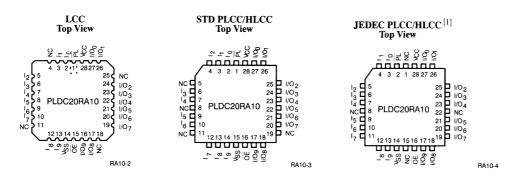

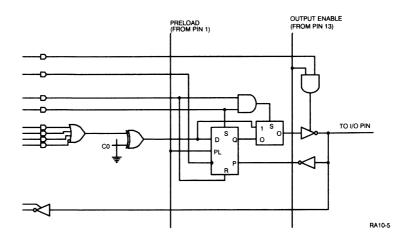

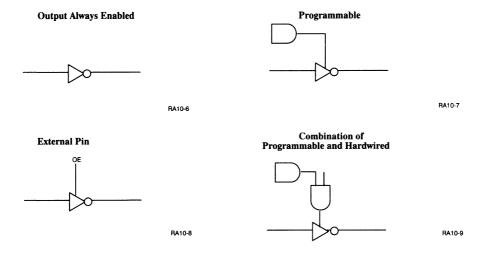

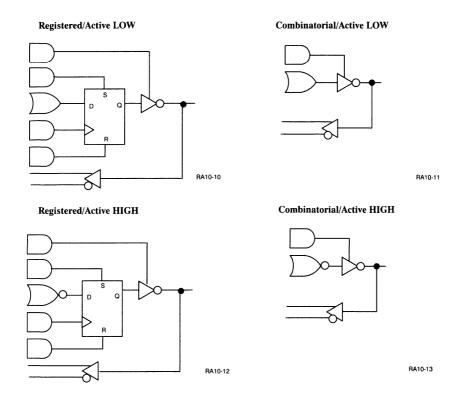

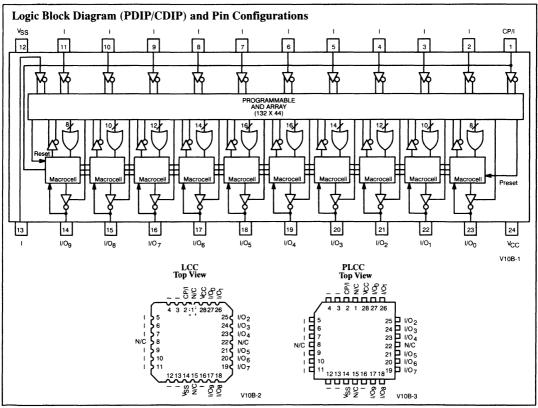

| PLDC20RA10                 | Reprogrammable Asynchronous CMOS Logic Device         |

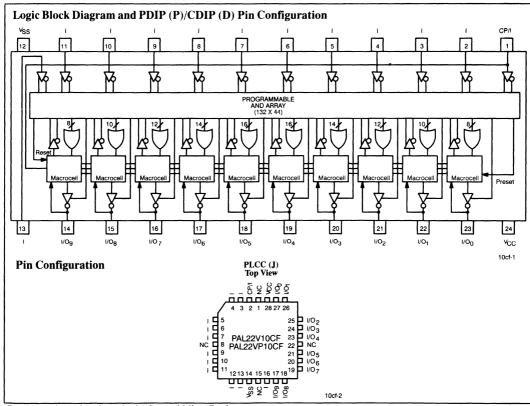

| PALC22V10                  | Reprogrammable CMOS PAL Device                        |

| PALC22V10B                 | Reprogrammable CMOS PAL Device                        |

| PAL22V10C                  | Universal PAL Device                                  |

| PAL22VP10C                 | Universal PAL Device                                  |

| PAL22V10CF                 | Universal PAL Device                                  |

| PAL22VP10CF                | Universal PAL Device                                  |

| PALC22V10D                 | Flash Erasable, Reprogrammable CMOS PAL Device        |

| PAL22V10G                  | Universal PAL Device                                  |

| PAL22VP10G                 | Universal PAL Device                                  |

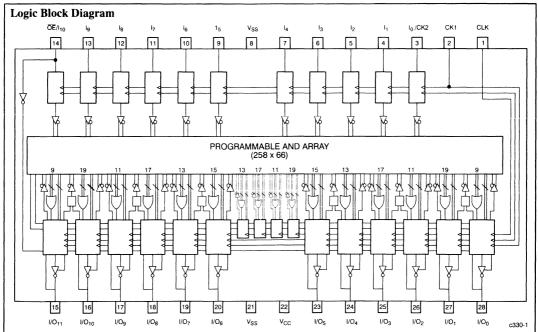

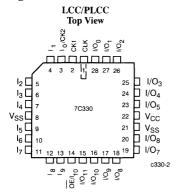

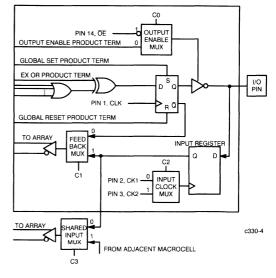

| CY7C330                    | CMOS Programmable Synchronous State Machine           |

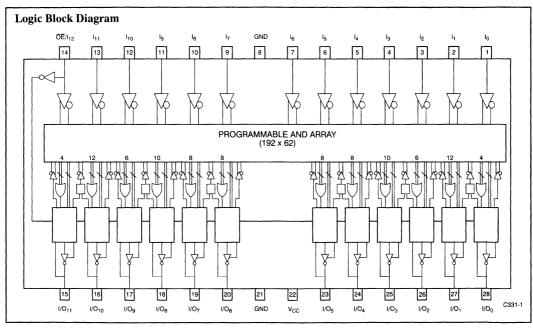

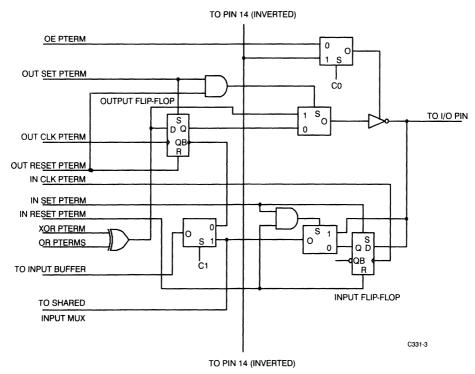

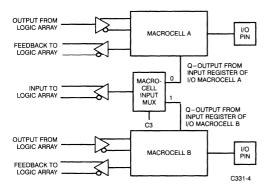

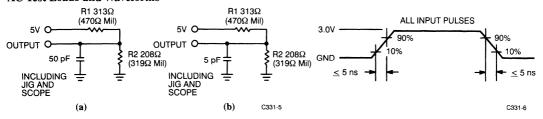

| CY7C331                    | Asynchronous Registered EPLD                          |

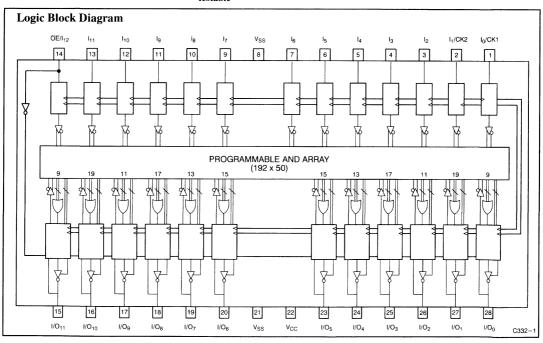

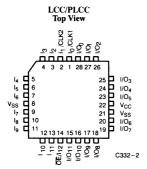

| CY7C332                    | Registered Combinatorial EPLD                         |

| CY7C335                    | Universal Synchronous EPLD                            |

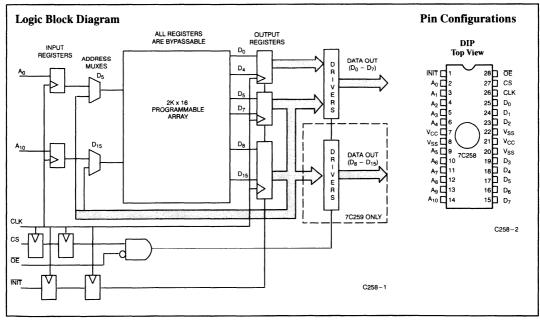

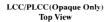

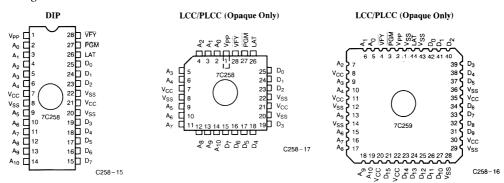

| CY7C258                    | 2K x 16 Reprogrammable State Machine PROM             |

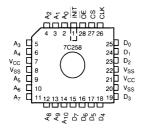

| CY7C259                    | 2K x 16 Reprogrammable State Machine PROM             |

| CPLDs (Complex PLD         | s)                                                    |

| Device                     | Description                                           |

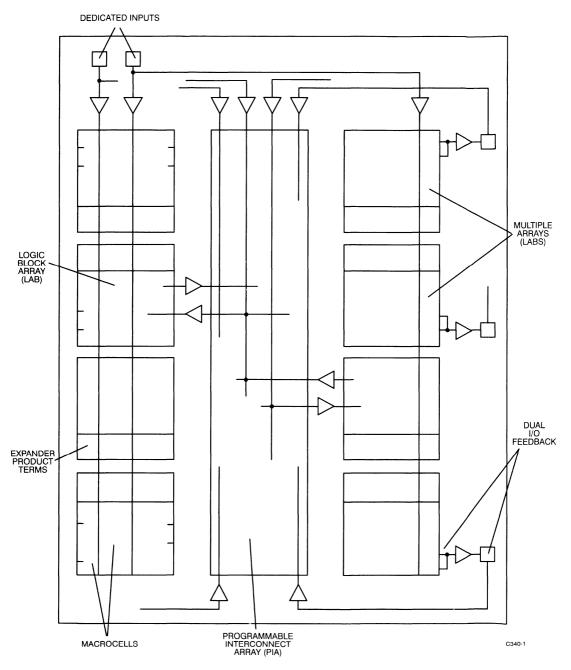

| CY7C340 EPLD Family        | Multiple Array Matrix High-Density EPLDs              |

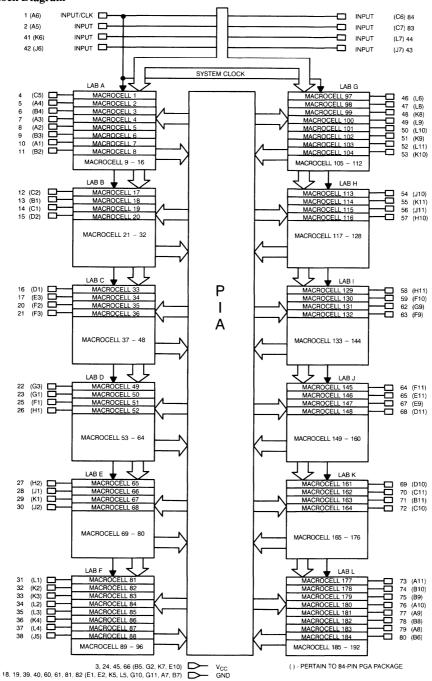

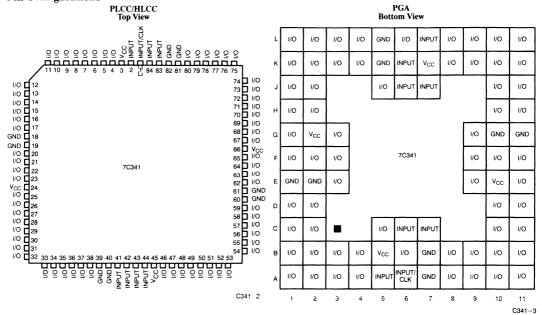

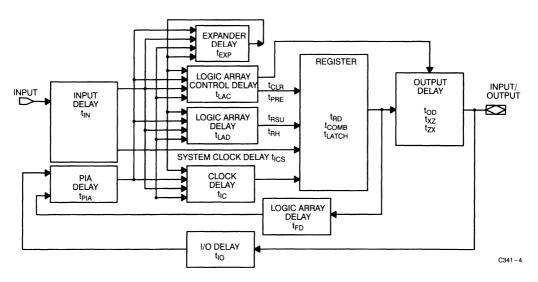

| CY7C341                    | 192-Macrocell MAX EPLD                                |

| CY7C341B                   | 192-Macrocell MAX EPLD                                |

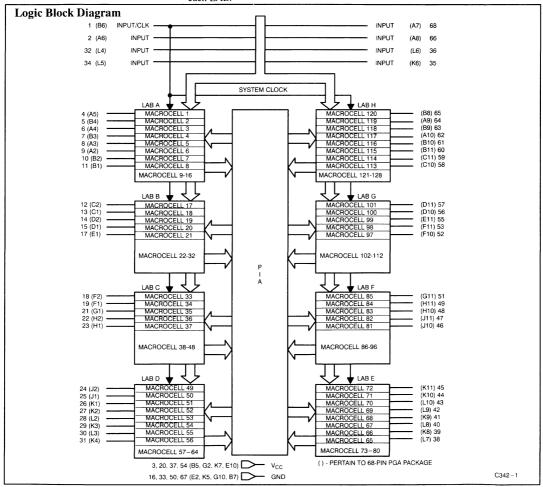

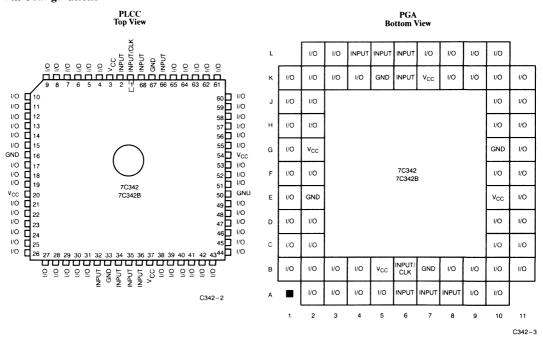

| CY7C342                    | 128-Macrocell MAX EPLD                                |

| CY7C342B                   | 128-Macrocell MAX EPLD 3-24                           |

| CY7C343                    | 64-Macrocell MAX EPLD                                 |

| CY7C343B                   | 64-Macrocell MAX EPLD                                 |

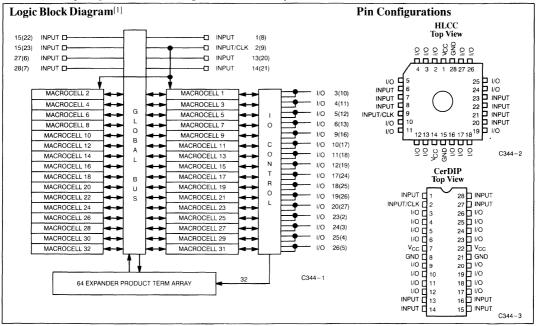

| CY7C344                    | 32-Macrocell MAX EPLD                                 |

| CY7C344B                   | 32-Macrocell MAX EPLD 3-58                            |

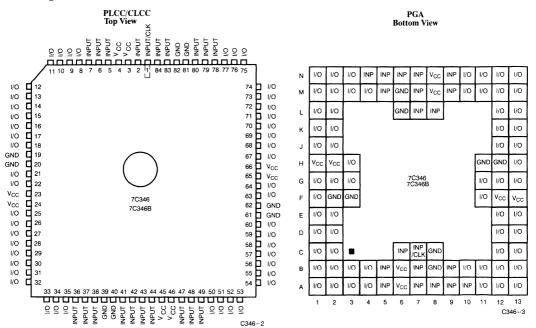

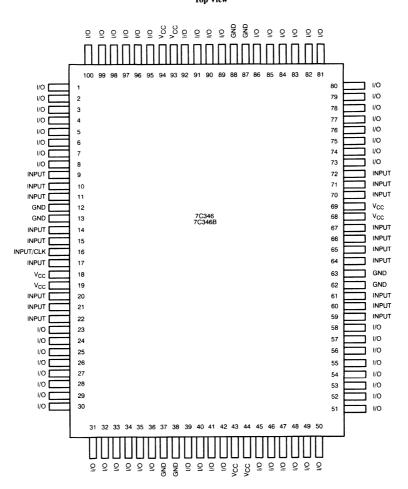

| CY7C346                    | 128-Macrocell MAX EPLD 3-73                           |

| CY7C346B                   | 128-Macrocell MAX EPLD                                |

| CPLDs (Complex PLD                                                                                                                                                                                           | Ds) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page Number                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

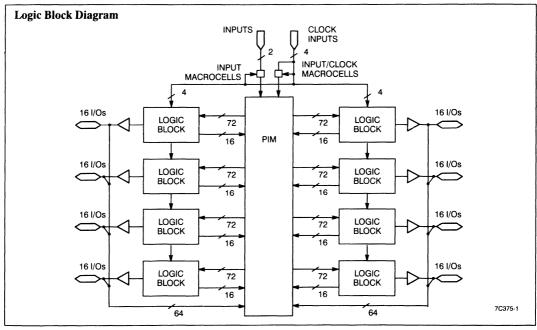

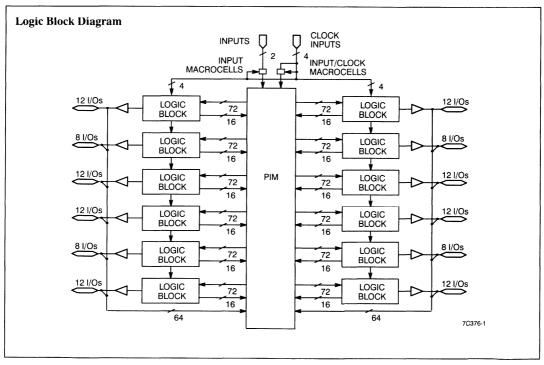

| Device<br>CY7C361<br>FLASH370 CPLD Family<br>CY7C371<br>CY7C372<br>CY7C373<br>CY7C374<br>CY7C375<br>CY7C376<br>CY7C377                                                                                       | Description Ultra High Speed State Machine EPLD High-Density Flash CPLDs 32-Macrocell Flash CPLD 64-Macrocell Flash CPLD 128-Macrocell Flash CPLD 128-Macrocell Flash CPLD 128-Macrocell Flash CPLD 192-Macrocell Flash CPLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-91 3-92 3-99 3-107 3-115 3-125 3-135 3-146        |

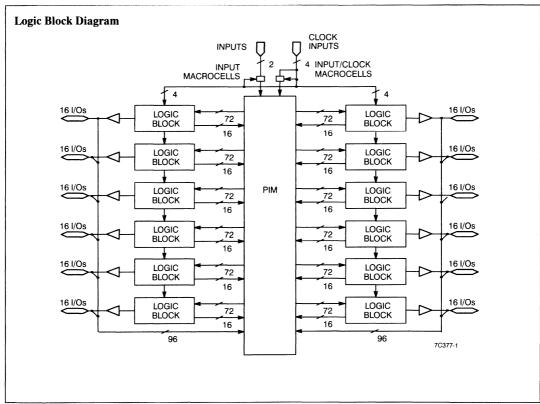

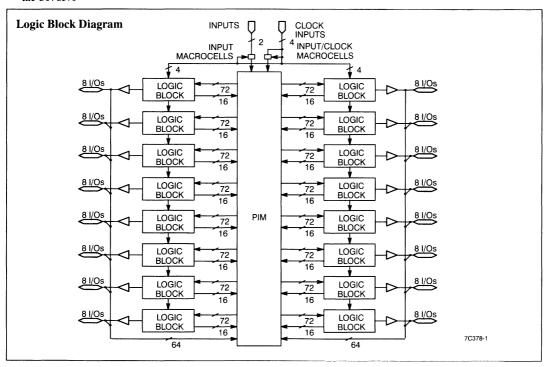

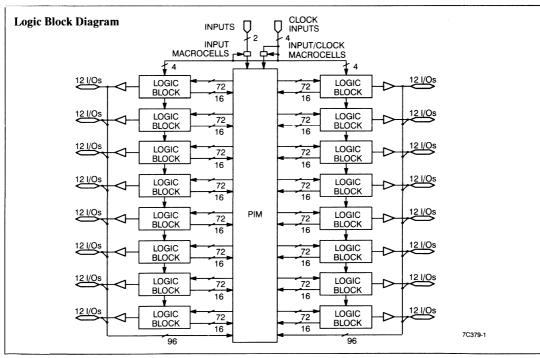

| CY7C378<br>CY7C379                                                                                                                                                                                           | 256-Macrocell Flash CPLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-148                                               |

| FPGAs (Field Progran                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

| Device                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

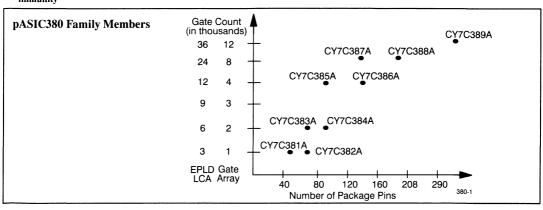

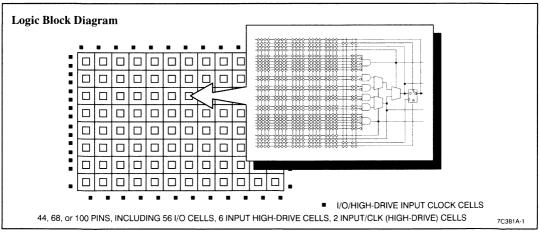

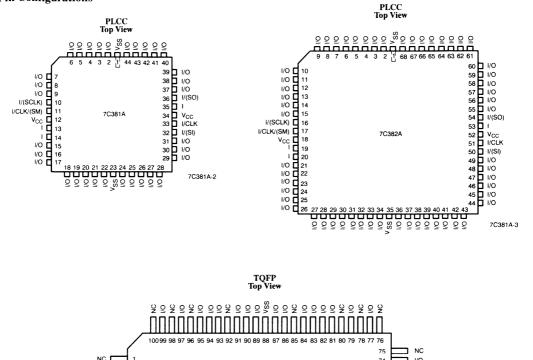

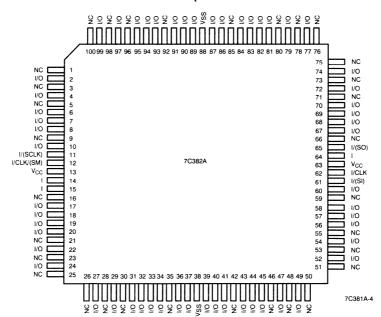

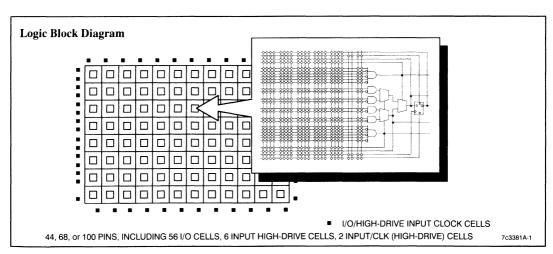

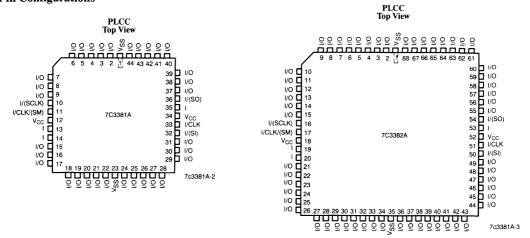

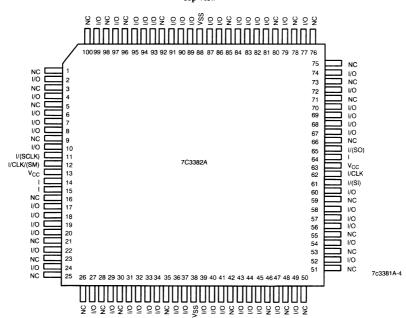

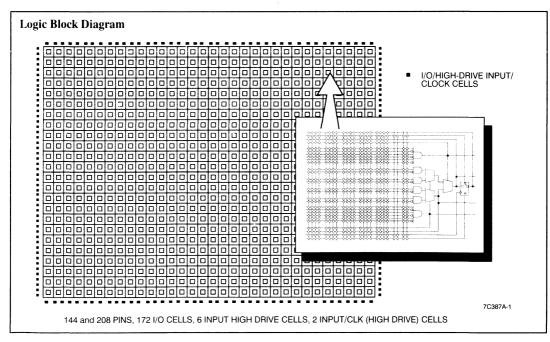

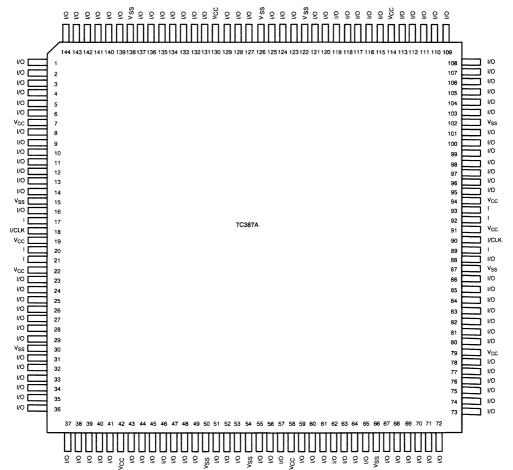

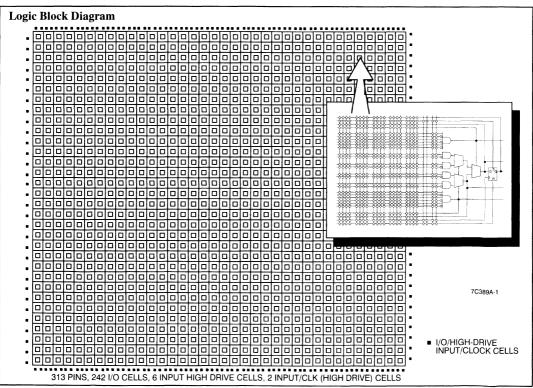

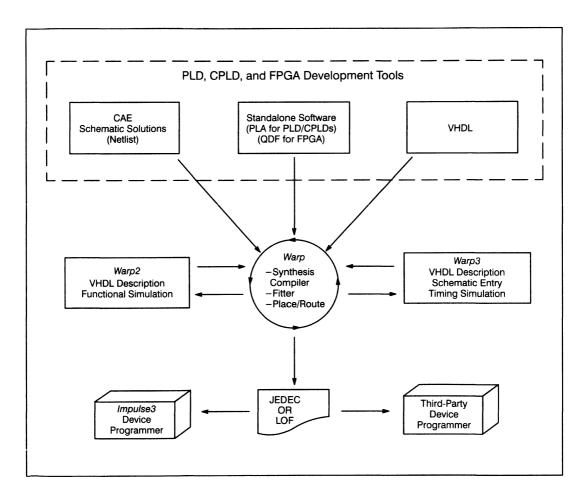

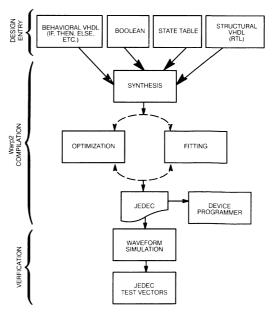

| pASIC380 Family CY7C381A CY7C382A CY7C382A CY7C3881A CY7C383A CY7C383A CY7C385A CY7C386A CY7C387A CY7C388A CY7C389A  Software PLD, CPLD, and FPGA De Device Warp2 CY3120/CY3125 Warp3 CY3130/CY3135 Impulse3 | Very High Speed CMOS FPGAs  Very High Speed 1K (3K) Gate CMOS FPGA  Very High Speed 1K (3K) Gate CMOS FPGA  3.3V High Speed 1K (3K) Gate CMOS FPGA  3.3V High Speed 1K (3K) Gate CMOS FPGA  Very High Speed 2K (6K) Gate CMOS FPGA  Very High Speed 2K (6K) Gate CMOS FPGA  Very High Speed 4K (12K) Gate CMOS FPGA  Very High Speed 4K (12K) Gate CMOS FPGA  Very High Speed 4K (12K) Gate CMOS FPGA  Very High Speed 8K (24K) Gate CMOS FPGA  Very High Speed 8K (24K) Gate CMOS FPGA  Very High Speed 8K (24K) Gate CMOS FPGA  Very High Speed 12K (36K) Gate CMOS FPGA | 4-8 4-8 4-17 4-17 4-25 4-25 4-34 4-34 4-45 4-45 5-1 |

| <b>Quality and Reliability</b>                                                                                                                                                                               | y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |

| pASIC380 Family Reliability<br>Power Characteristics of Cyl<br>Quality, Reliability, and Pro-                                                                                                                | ation  ry Report  ry Press Programmable Logic Products  cocess Flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |

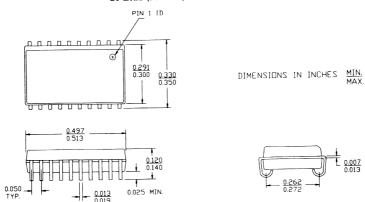

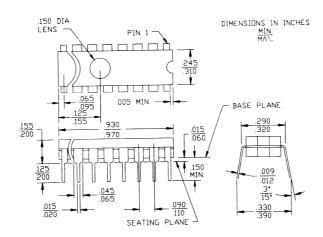

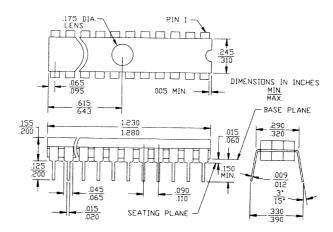

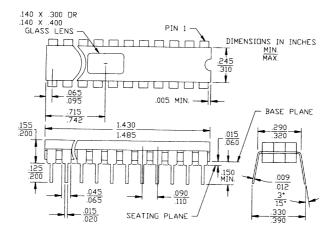

| Packages                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

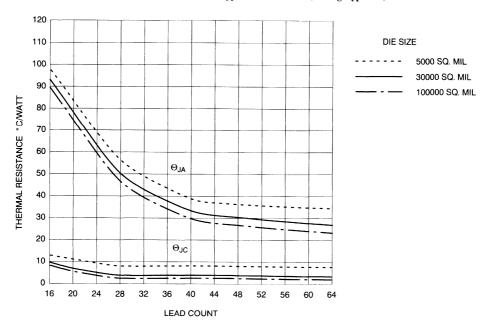

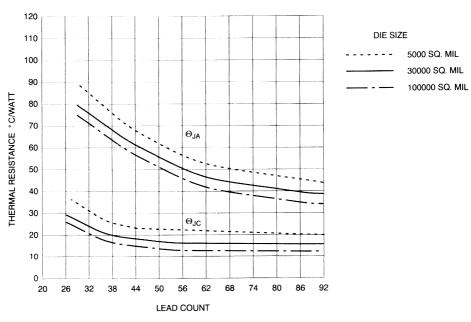

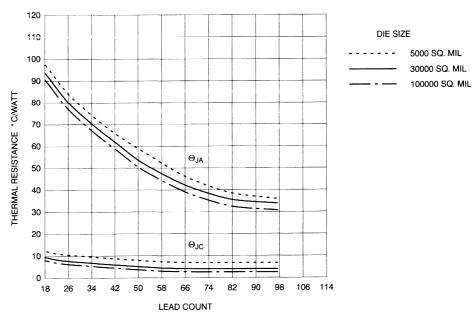

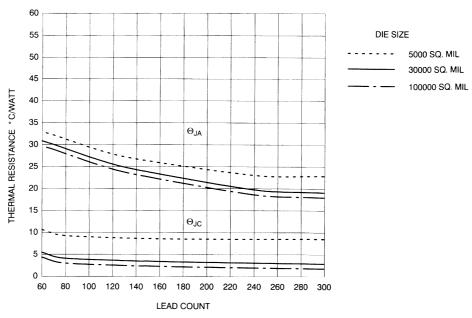

| Thermal Management and C                                                                                                                                                                                     | Component Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

#### Sales Representatives and Distributors

Direct Sales Offices North American Sales Representatives International Sales Representatives Distributors

### **Numeric Device Index**

| Device Number        | Description                                           | Page Number |

|----------------------|-------------------------------------------------------|-------------|

| CY3120/CY3125        | Warp2 VHDL Compiler for PLDs, CPLDs, and FPGAs        | 5-2         |

| CY3130/CY3135        | Warp3 VHDL Development System for PLDs and FPGAs      |             |

| CY7C330              | CMOS Programmable Synchronous State Machine           |             |

| CY7C331              | Asynchronous Registered EPLD                          |             |

| CY7C332              | Registered Combinatorial EPLD                         |             |

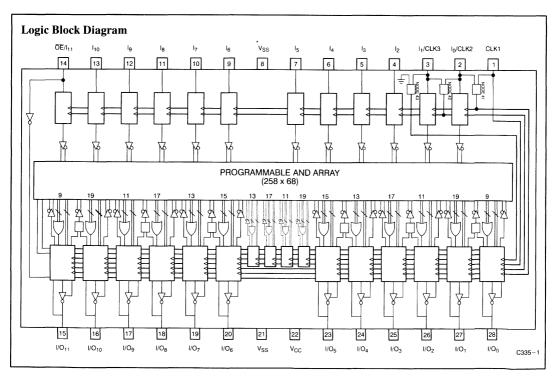

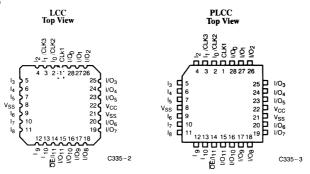

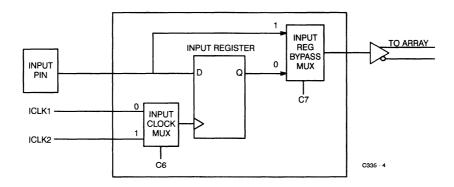

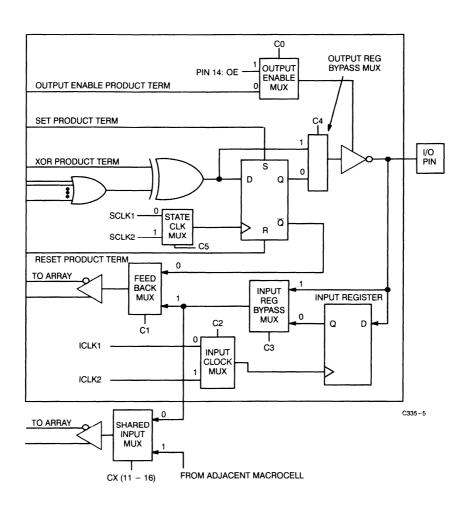

| CY7C335              | Universal Synchronous EPLD                            |             |

| CY7C258              | 2K x 16 Reprogrammable State Machine PROM             |             |

| CY7C259              | 2K x 16 Reprogrammable State Machine PROM             |             |

| CY7C340 EPLD Family  | Multiple Array Matrix High-Density EPLDs              |             |

| CY7C341              | 192-Macrocell MAX EPLD                                |             |

| CY7C341B             | 192-Macrocell MAX EPLD                                |             |

| CY7C342              | 128-Macrocell MAX EPLDs                               |             |

| CY7C342B             | 128-Macrocell MAX EPLDs                               |             |

| CY7C342B             | 64-Macrocell MAX EPLD                                 |             |

| CY7C343B             | 64-Macrocell MAX EPLD                                 |             |

| CY7C344              | 32-Macrocell MAX EPLD                                 |             |

| CY7C344B             | 32-Macrocell MAX EPLD                                 |             |

| CY7C346              | 128-Macrocell MAX EPLDs                               |             |

| CY7C346B             | 128-Macrocell MAX EPLDs                               |             |

|                      |                                                       |             |

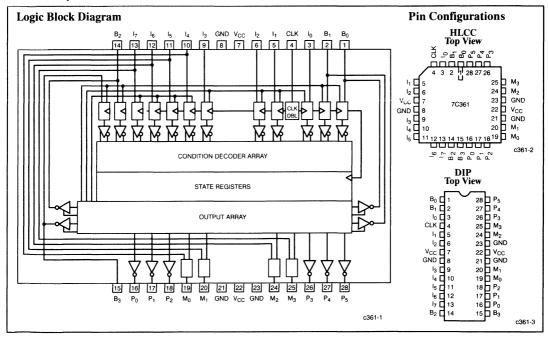

| CY7C361              | Ultra High Speed State Machine EPLD                   |             |

| CY7C371              | 32-Macrocell Flash CPLD                               |             |

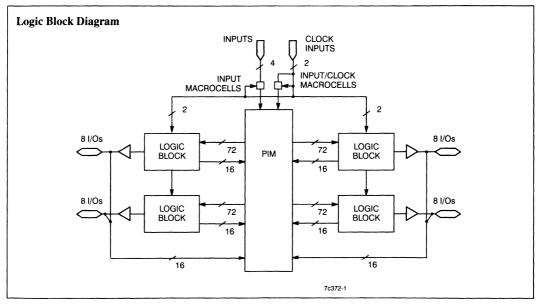

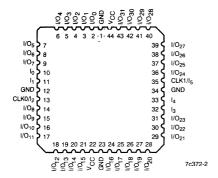

| CY7C372              | 64-Macrocell Flash CPLD                               |             |

| CY7C373              | 64-Macrocell Flash CPLD                               |             |

| CY7C374              | 128-Macrocell Flash CPLD                              |             |

| CY7C375              | 128-Macrocell Flash CPLD                              |             |

| CY7C376              | 192-Macrocell Flash CPLD                              |             |

| CY7C377              | 192-Macrocell Flash CPLD                              |             |

| CY7C378              | 256-Macrocell Flash CPLD                              |             |

| CY7C379              | 256-Macrocell Flash PLD                               |             |

| CY7C381A             | Very High Speed 1K (3K) Gate CMOS FPGA                |             |

| CY7C382A             | Very High Speed 1K (3K) Gate CMOS FPGA                |             |

| CY7C3381A            | 3.3V High Speed 1K (3K) Gate CMOS FPGA                |             |

| CY7C3382A            | 3.3V High Speed 1K (3K) Gate CMOS FPGA                |             |

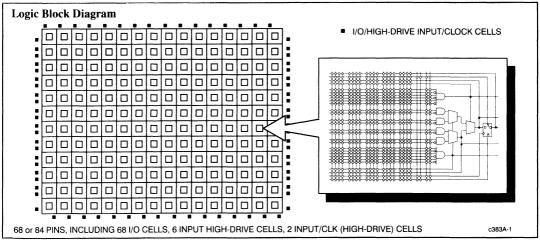

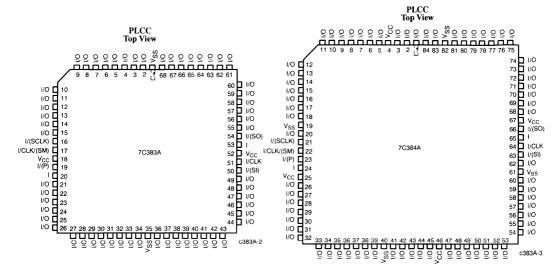

| CY7C383A             | Very High Speed 2K (6K) Gate CMOS FPGA                |             |

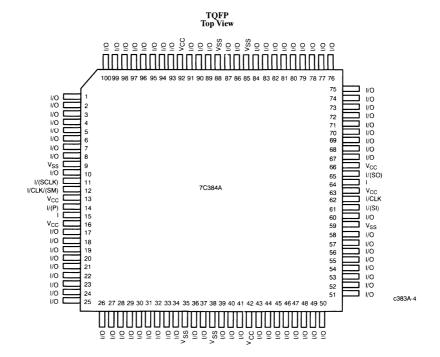

| CY7C384A             | Very High Speed 2K (6K) Gate CMOS FPGA                |             |

| CY7C385A             | Very High Speed 4K (12K) Gate CMOS FPGA               |             |

| CY7C386A             | Very High Speed 4K (12K) Gate CMOS FPGA               |             |

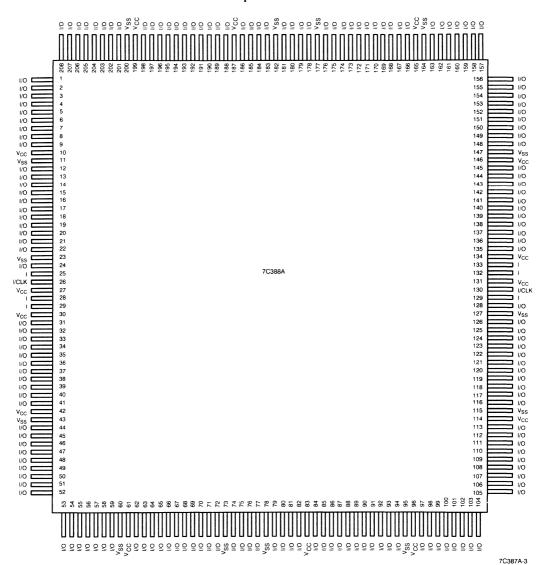

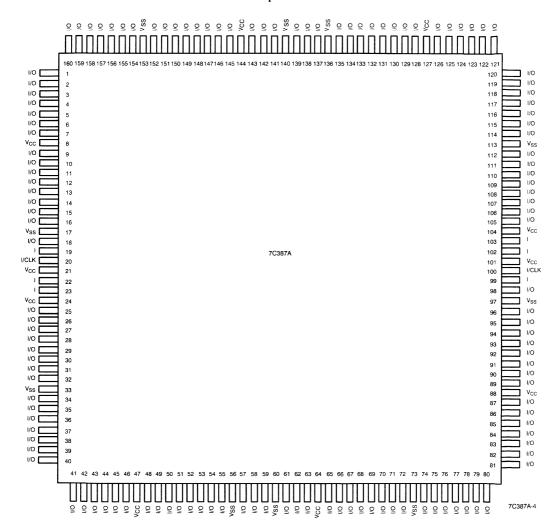

| CY7C387A             | Very High Speed 8K (24K) Gate CMOS FPGA               |             |

| CY7C388A             | Very High Speed 8K (24K) Gate CMOS FPGA               |             |

| CY7C389A             | Very High Speed 12K (36K) Gate CMOS FPGA              |             |

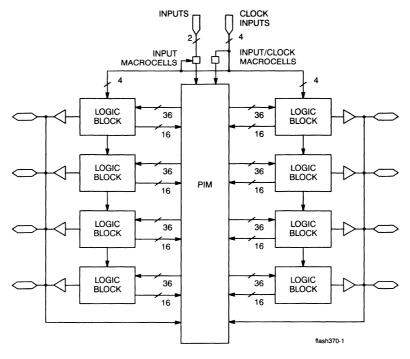

| FLASH370 CPLD Family | High-Density Flash CPLDs                              |             |

| Impulse3             | Device Programer                                      | 5-12        |

| PAL20 Series         | 4.5-ns, Industry-Standard PLDs 16L8, 16R8, 16R6, 16R4 |             |

| PALC20 Series        | Reprogrammable CMOS PALC 16L8, 16R8, 16R6, 16R4       | 2-16        |

| PAL22V10C            | Universal PAL Device                                  | 2-70        |

| PAL22VP10C           | Universal PAL Device                                  |             |

| PAL22V10CF           | Universal PAL Device                                  | 2-81        |

| PAL22VP10CF          | Universal PAL Device                                  |             |

| PAL22V10G            | Universal PAL Device                                  | 2-91        |

| PAL22VP10G           | Universal PAL Device                                  | 2-91        |

| PALC22V10            | Reprogrammable CMOS PAL Device                        | 2-68        |

| DAT CONTION          | Panragrammable CMOS BALD Daviga                       | 2 (0        |

### **Numeric Device Index**

| Device Number   | Description                                     | Page Number |

|-----------------|-------------------------------------------------|-------------|

| PALC22V10D      | Flash Erasable, Reprogrammable CMOS PAL Device  | 2-82        |

| PALCE16V8       | Flash Erasable, Reprogrammable CMOS PAL Device  | 2-30        |

| PALCE20V8       | Flash Erasable, Reprogrammable CMOS PAL Device  | 2-38        |

| pASIC380 Family | Very High Speed CMOS FPGAs                      | 4-1         |

| PLDC20G10       | CMOS Generic 24-Pin Reprogrammable Logic Device | 2–39        |

| PLDC20G10B      | CMOS Generic 24-Pin Reprogrammable Logic Device | 2-39        |

| PLD20G10C       | Generic 24-Pin PAL Device                       | 2-47        |

| PLDC20RA10      | Reprogrammable Asynchronous CMOS Logic Device   | 2-57        |

# General Information 1

### **Section Contents**

| General Product Information                                    | Page Number |

|----------------------------------------------------------------|-------------|

| Cypress Semiconductor Background                               | 1–1         |

| Ordering Information                                           | 1-4         |

| Cypress Semiconductor Bulletin Board System (BBS) Announcement | 1-5         |

| Application Notes Listing                                      | 1-6         |

| Product Selector Guide                                         | 1-7         |

| Product Line Cross Reference                                   | 1-9         |

| Military Overview                                              | 1-14        |

| Military Product Selector Guide                                | 1-15        |

| Military Ordering Information                                  | 1–13        |

#### **Cypress Semiconductor Background**

Cypress Semiconductor was founded in April 1983 with the stated goal of serving the high-performance semiconductor market. This market is served by producing the highest-performance integrated circuits using state-of-the-art processes and circuit design. Cypress is a complete semiconductor manufacturer, performing its own process development, circuit design, wafer fabrication, assembly, and test. The company went public in May 1986 and has been listed on the New York Stock Exchange since October 1988.

The initial semiconductor process, a CMOS process employing 1.2-micron geometries, was introduced in March 1984. This process is used in the manufacturing of Static RAMs and Logic circuits. In the third quarter of 1984, a 1.2-micron CMOS EPROM process was introduced for the production of programmable products. At the time of introduction, these processes were the most advanced production processes in the industry. Following the 1.2-micron processes, a 0.8-micron CMOS SRAM process was implemented in the first quarter of 1986, and a 0.8-micron EPROM process in the third quarter of 1987.

In keeping with the strategy of serving the high-performance markets with state-of-the-art integrated circuits, Cypress introduced two new processes in 1989. These were a bipolar submicron process, targeted for ECL circuits, and a BiCMOS process to be used for most types of TTL and ECL circuits.

The circuit design technology used by Cypress is also state of the art. This design technology, along with advanced process technology, allows Cypress to introduce the fastest, highest-performance circuits in the industry. Cypress's offers products in four divisions: the Static Memory Division, the Programmable Products Division, the Computation Products Division, and the Data Communications Division.

#### **Static Memories Division**

Cypress is a market-leading supplier of SRAMs, providing a wide range of SRAM memories for leading companies worldwide. SRAMs are used in high-performance personal computers, workstations, telecommunications systems, industrial systems, instrumentation devices, and networking products. Cypress's lower production cost structure allows the company to compete effectively in the high-volume personal computer and workstation market for SRAMs, including providing cache RAMs to support today's high-performance microprocessors, such as Pentium  $^{\infty}$ , and PowerPC  $^{\infty}$ . This business, combined with upcoming low-voltage products for the cellular communications, portable instrument, and laptop/notebook PC markets, positions Cypress for future success in this key product area.

Multichip modules is a fast-growing market segment that consists of multiple semiconductor chips mounted in packages that can be inserted in a computer circuit board. Cache modules for personal computers are the mainstay of this product line, and Cypress has announced major design wins for these products in IBM's PS/ValuePoint ™ line of PCs, and in Apple Computer's highest performing Power Macintosh ™ products.

#### **Programmable Products Division**

With increasing pressure on system designers to bring products to market more quickly, programmable logic devices (PLDs) are becoming extremely popular. PLDs are logic control devices that can be easily programmed by engineers in the field, and later erased and reprogrammed. This allows the designers to make

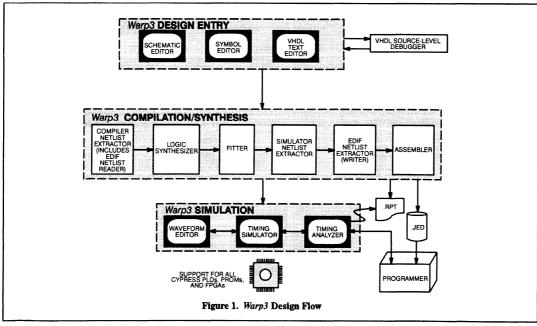

key changes to their systems very late in the development cycle to ensure competitive advantage. Used extensively in an wide range of applications, PLDs constitute a large and growing market. Cypress's UltraLogic product line addresses the high-density programmable logic market. UltraLogic includes the pASIC380 family of field-programmable gate arrays (FPGAs), the industry's fastest. It also includes the highest performance complex PLDs, the FLASH370 family. Both of these product families are supported by Cypress's VHDL (Very high-speed integrated circuit Hardware Description Language) based Warp3 the industry's most advanced software design tool. Cypress pioneered the use of VHDL for PLD programming, and Warp software is a key factor in the company's overall success in the PLD market.

Cypress is a leading provider of the industry-standard 22V10 PLD with a wide range of offerings including a BiCMOS 22V10 at 5 ns. Cypress is committed to competing in all ranges of the PLD market, with small devices, the MAX <sup>™</sup> CY7C340 EPLD ine, and the UltraLogic products. To support these products, Cypress offers one of the industry's broadest range of programming tools and software for the programming of its PLDs.

Cypress provides one of the industry's broadest ranges of CMOS EPROMs and PROMs. Cypress owns a large share of the high-speed CMOS PROM market, and with its new cost structure, is effectively penetrating the mainstream EPROM market with a popular 256 Kbit EPROM and the introduction of the world's fastest 1 Megabit EPROM at 25 ns.

FCT Logic products are used in bus interface and data buffering applications in almost all digital systems. With the addition of the FCT logic product line, Cypress now offers over 46 standard logic and bus interface functions. The products are offered in the second generation FCT-T format, which is pin-compatible with the older FCT devices, but adds TTL (transistor-to-transistor logic) outputs for significantly lower ground bounce and improved system noise immunity. Cypress also offers the most (FCT2-T) to further lower ground bounce with no speed loss. Included in the new product family is the CYBUS3384, a bus switch that enables bidirectional data transfer between multiple bus systems or between 5 volt and 3.3 volt devices. This broad product offering is produced on Cypress's high-volume, CMOS manufacturing lines.

#### **Data Communications Division**

This is an especially significant area for Cypress since it represents a more market-driven orientation for the company in a fast-growing market segment. As part of the new company strategy, Cypress has dedicated this product line to serve the highspeed data communications market with a range of products from the physical connection layer to system-level solutions. HOTLink<sup>™</sup>, high-speed, point-to-point serial communications chips have been well received. HOTLink, along with the recently announced SONET./SDS Serial Transceiver (SST™), address the fast-growing market segments of Asynchronous Transfer Mode (ATM) and Fibre Channel communications. The data communications division encompasses related products including RoboClock, a programmable skew clock buffer that adjusts complex timing control signals for a broad range of systems. The division also offers a broad range of First-In, First-Out (FIFO) memories, used to communicate data between systems operating at different frequencies, and Dual-Port Memories, used to distribute data to two different systems simultaneously.

#### **Computation Products Division**

This division focuses on the high-volume, high-growth market surrounding the desktop computer. It is the second of Cypress's market-oriented divisions. The division includes timing technology products offered through Cypress's IC Designs Subsidiary in Kirkland, Washington, and a new line of PC chipsets. IC Designs products are used widely in personal computers and disk drives, and the product line provides Cypress with major inroads into these growing markets. IC Designs clock oscillators control the intricate timing of all aspects of a computer system, including signals for the computer's central processing unit (CPU), keyboard, disk drives, system bus, serial port, and real-time clock. They replace all of the metal can oscillators used in the system. This product line includes QuiXTAL™ — a programmable metal can oscillator that replaces individual oscillators used to control timing signals in virtually every type of electronics equipment. Cypress's chipset offerings include products for 486-based personal computers, as well as PCI local bus controllers for graphics and multimedia desktop applications. Cypress has announced plans to introduce a low-power, 3.3 volt chipset for the Pentium P54C, as well as P54C bus controller.

#### **Cypress Facilities**

Situated in California's Silicon Valley (San Jose), Round Rock (Austin), Texas, and Bloomington, Minnesota, Cypress houses R&D, design, wafer fabrication, and administration. There are additional Cypress Design Centers in Starkville, Mississippi, Colorado Springs, Colorado, and the United Kingdom, and a PLD software design group in Beaverton, Oregon. The facilities are designed to the most demanding technical and environmental specifications in the industry. At the Texas and Minnesota facilities, the entire wafer fabrication area is specified to be a Class 1 environment. This means that the ambient air has less than 1 particle of greater than 0.2 microns in diameter per cubic foot of air. Other environmental considerations are carefully insured: temperature is controlled to a  $\pm 0.1$  degree Fahrenheit tolerance; filtered air is completely exchanged more than 10 times each minute throughout the fab; and critical equipment is situated on isolated slabs to minimize vibration

Attention to assembly is equally critical. Cypress manufactures 100 percent of our wafers in the United States, at our front-end fabrication sites in California (San Jose), Minnesota (Bloomington), and Texas (Round Rock). Cypress Texas, our largest fab, and Cypress Minnesota, our newest fab, are both Class 1 facilities.

To improve our global competitiveness, we chose to move most of our back-end assembly, test, and mark operations to a facility in Thailand. Be assured that Cypress's total quality commitment extends to the new site—Cypress Bangkok.

The move to Bangkok consummated an intense search by Cypress for a world-class, environmentally sophisticated facility that we could bring on line quickly. The Cypress search team scrutinized fifteen manufacturing facilities in five countries and chose a site managed by Alphatec Electronics Co., Ltd., a privately owned, entrepreneurial company promoted by the Thailand Board of Investment. Cypress Bangkok occupies almost 25,000 square feet—a significant portion of the manufacturing floor space available within the facility. The full facility at Bangkok occupies more than 85,000 square feet on a site that encompasses 25 acres—sufficient room for expansion to a number of buildings in a campus-like setting.

Manufacturing at the site since 1990 with a charter to specialize in IC packaging, the Alphatec facility has almost a century of person-years experience working for U.S. semiconductor suppliers. Thoroughly modern, MIL 883-certified, and with fully developed administrative, logistic, and manufacturing systems in place, the facility has earned an exceptional reputation for hermetic assembly and out-going quality.

Cypress San Jose maintains complete management control of Cypress Bangkok's assembly, test, mark, and ship operations within the facility, thus assuring complete continuity of San Jose's back-end operations and quality.

Cypress has added Tape Automated Bonding (TAB) to its package offering. TAB, a surface-mount packaging technology, provides the densest lead and package footprint available for fully tested die.

From Cypress's facility in Minnesota, a VME Bus Interface Products group has been in operation since the acquisition of VTC's fab in 1990. Cypress manufactures VIC and VAC VME devices on the 0.8 micron CMOS process.

The Cypress motto has always been "only the best—the best facilities, the best equipment, the best employees . . . all striving to make the best CMOS, BiCMOS, and bipolar products."

#### **Cypress Process Technology**

In the last decade, there has been a tremendous need for highperformance semiconductor products manufactured with a balance of SPEED, RELIABILITY, and POWER. Cypress Semiconductor overcame the classically held perceptions that CMOS was a moderate-performance technology.

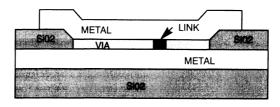

Cypress initially introduced a 1.2-micron "N" well technology with double-layer poly and a single-layer metal. The process employed lightly doped extensions of the heavily doped source and drain regions for both "N" and "P" channel transistors for significant improvement in gate delays. Further improvements in performance, through the use of substrate bias techniques, have added the benefit of eliminating the input and output latch-up characteristics associated with older CMOS technologies.

Cypress pushed process development to new limits in the areas of PROMs (Programmable Read Only Memory) and EPLDs (Erasable Programmable Logic Devices). Both PROMs and EPLDs have existed since the early 1970s in a bipolar process that employed various fuse technologies and was the only viable high-speed nonvolatile process available. Cypress PROMs and EPLDs use EPROM technology, which has been in use in MOS (Metal Oxide Silicon) since the early 1970s. EPROM technology has traditionally emphasized density while forsaking performance. Through improved technology, Cypress produced the first high-performance CMOS PROMs and EPLDs, replacing their bipolar counterparts.

To maintain our leadership position in CMOS technology, Cypress introduced a sub-micron technology in 1987. This 0.8 micron breakthrough made Cypress's CMOS one of the most advanced production processes in the world. The drive to maintain leadership in process technology has not stopped with the 0.8-micron devices. Cypress introduced a 0.65-micron process in 1991. A 0.5-micron process is currently in production.

Although not a requirement in the high-performance arena, CMOS technology substantially reduces the power consumption for any device. This improves reliability by allowing the device to operate at a lower die temperature. Now higher levels of integration are possible without trading performance for power. For in-

stance, devices may now be delivered in plastic packages without any impact on reliability.

While addressing the performance issues of CMOS technology, Cypress has not ignored the quality and reliability aspects of technology development. Rather, the traditional failure mechanisms of electrostatic discharge (ESD) and latch-up have been addressed and solved through process and design technology innovation.

ESD-induced failure has been a generic problem for many high-performance MOS and bipolar products. Although in its earliest years, MOS technology experienced oxide reliability failures, this problem has largely been eliminated through improved oxide growth techniques and a better understanding of the ESD problem. The effort to adequately protect against ESD failures is perturbed by circuit delays associated with ESD protection circuits. Focusing on these constraints, Cypress has developed ESD protection circuitry specific to 1.2-, 0.8-, 0.65-, and 0.5-micron CMOS process technology. Cypress products are designed to withstand voltage and energy levels in excess of 2001 volts and 0.4 milli-joules.

Latch-up, a traditional problem with CMOS technologies, has been eliminated through the use of substrate bias generation techniques, the elimination of the "P" MOS pull-ups in the output drivers, the use of guardring structures and care in the physical layout of the products.

Cypress has also developed additional process innovations and enhancements: multilayer metal interconnections, advanced metal deposition techniques, silicides, exclusive use of plasma for etching, and 100-percent stepper technology with the world's most advanced equipment.

Cypress has developed a BiCMOS technology to augment the capabilities of the Cypress CMOS processes. The new BiCMOS technology is based on the Cypress 0.8-micron CMOS process for enhanced manufacturability. Like CMOS, the process is scalable, to take advantage of finer line lithography. Where speed is critical, Cypress BiCMOS allows increased transistor performance. It also allows reduced power in the non-speed critical sections of the design to optimize the speed/power balance. The BiCMOS process makes memories and logic operating up to 400 MHz possible.

Cypress technologies have been carefully designed, creating products that are "only the best" in high-speed, excellent reliability, and low power.

IBM PC and IBM ESCON are registered trademarks of International Business Machines Corporation. QuickPro II, HOTLink, and Warp2 are trademarks of Cypress Semiconductor Corporation.

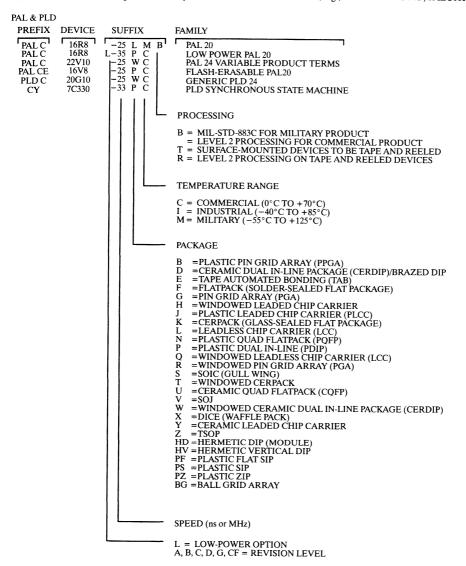

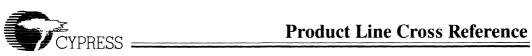

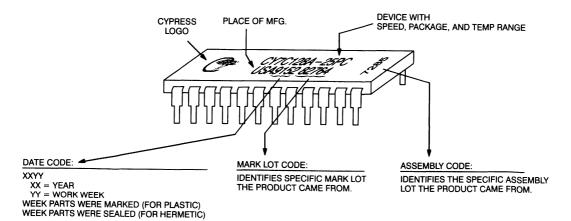

In general, the valid ordering codes for all products follow the format below; e.g., CY7C128-45DMB, PALC16R8L-35PC

Cypress FSCM #65786

#### Cypress Semiconductor Bulletin Board System (BBS) Announcement

Cypress Semiconductor supports a 24-hour electronic Bulletin Board System (BBS) that allows Cypress Applications to better serve our customers by allowing them to transfer files to and from the BBS.

The BBS is set up to serve in multiple ways. One of its purposes is to allow customers to receive the most recent versions of programming software. Another is to allow the customers to send PLD programming files that they are having trouble with to the BBS. Cypress Applications can then find the errors in the files, correct them, and place them back on the BBS for the customer to download. The customer may also ask questions in our open forum message area. The sysop (system operator) will forward these questions to the appropriate applications engineer for an answer. The answers then get posted back into the forum. The BBS also allows the customer to communicate with their local FAE electronically, and to download both application notes and the latest versions of selected datasheets.

#### **Communications Set-Up**

The BBS uses a USRobotics HST Dual Standard modems capable of 14.4-Kbaud rates without compression and rates upwards of 19.2-Kbaud with compression. It is compatible with CCITT V.32 bis, V.32, V.22 (2400-baud), Bell 212A (1200-baud), CCITT V.42, and CCITT V.42 bis. It also handles MNP levels 2, 3, 4, and 5.

To call the BBS, set your communication package parameters as follows:

Baud Rate: 1200 baud to 19.2 Kbaud. Max. is determined by your modem.

Data Bits: 8 Parity: None (N) Stop Bits: 1

In the U.S. the phone number for the BBS is (408) 943-2954. In Japan the BBS number is 81-423-69-8220. In Europe the BBS number is 49-810-62-2675. These numbers are for transmitting data only.

If the line is busy, please retry at a later time. When you access the BBS, an initial screen with the following statement will appear:

Rybbs Bulletin Board

After you choose the graphics format you want to use, the system will ask for your first and last name. If you are a first-time user, you will be asked a few questions for the purposes of registration. Otherwise you will be asked for your password, and then you will be logged onto the BBS, which is completely menu driven.

#### **Downloading Application Notes and Datasheets**

A complete listing of files that may be downloaded is included on the BBS. Application notes and selected datasheets are available for downloading in two formats, PCL and Postscript. An "hp" in front of the file name indicates it is a PCL file and can be downloaded to Hewlett-Packard LaserJets and compatible printers. Files without the hp preceding them are in Postscript and can be downloaded to any Postscript printer.

If you have any problems or questions regarding the BBS, please contact Cypress Applications at (408) 943-2821 (voice).

Contact a Cypress representative or use the Cypress Bulletin Board System to get copies of the application notes listed here.

ABEL 4.0/4.1 and the CY7C330, CY7C331, and CY7C332

Bus-Oriented Maskable Interrupt Controller

**CMOS PAL Basics**

CY7C330 as a Multi-Channel Mbus Arbiter

CY7C331 Asynchronous Self-Timed VMEbus Requestor

CY7C344 as a Second-Level Cache Controller for the 80486

Design Tips for Advanced Max Users

Designing a Multiprocessor Interrupt Distribution Unit with MAX

DMA Control Using the CY7C342 MAX EPLD

FDDI Physical Connection Management Using the CY7C330

FIFO RAM Controller with Programmable Flags

Interfacing PROMs and RAMs to DSP Using Cypress MAX Products

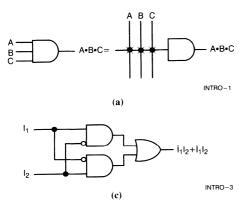

Introduction to Programmable Logic

PAL Design Example: A GCR Encoder/Decoder

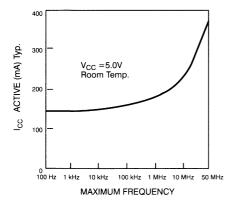

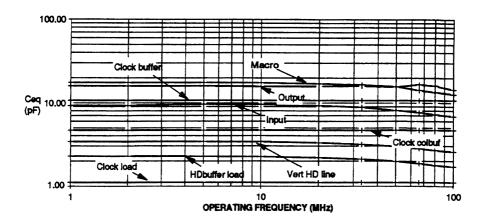

pASIC380 Power vs. Operating Frequency

PLD-Based Data Path For SCSI-2

State Machine Design Considerations and Methodologies

T2 Framing Circuitry

Understanding the CY7C330 Synchronous EPLD

Using ABEL to Program the Cypress 22V10

Using ABEL to Program the CY7C330

Using ABEL 3.2 to Program the CY7C331

Using CUPL with Cypress PLDs

Using Log/IC to Program the CY7C330

Using One-Hot-State Coding to Accelerate a MAX State Machine

Using the CY7C330 in Closed-Loop Servo Control

Using the CY7C331 as a Waveform Generator

Using the CY7C344 with the PLD ToolKit

Are Your PLDs Metastable?

State Machine Design Considerations and Methodologies

Designing with the CY7C335 and Warp2 VHDL Compiler

The FLASH370 Family Of CPLDs and Designing with Warp2

Implementing a Reframe Controller for the CY7B933 HOTLink Receiver in a CY7C371 CPLD

Architectures and Technologies for FPGAs

Designing with FPGAs

An Introduction to Cypress's 380 Family of FPGAs and the Warp3 Design Tool

CY7C380 Family Quick Power Calculator

Using Scan Mode on pASIC380 For In-Circuit Testing

Getting Started Converting .ABL Files to VHDL

Top-Down Design Methodology With VHDL (Designing an Interrupt Controller)

Abel-HDL vs. IEEE-1076 VHDL

VHDL Techniques for Optimal Design Fitting

Describing State Machines with Warp2 VHDL

Using Hierarchical VHDL Design

Glossary '93

Glossary '94

#### **PLDs**

| Size    | Organization                      | Pins | Part Number | Speed (ns)                                             | I <sub>CC</sub> /I <sub>SB</sub><br>(mA @ ns) | Packages                  | Availability |

|---------|-----------------------------------|------|-------------|--------------------------------------------------------|-----------------------------------------------|---------------------------|--------------|

| PAL20   | 16L8                              | 20   | PAL16L8     | $t_{PD} = 4.5/5/7$                                     | 180                                           | D,J,P                     | Now          |

| PAL20   | 16R8                              | 20   | PAL16R8     | $t_{S/CO} = 2.5/4.5, 2.5/5, 3.5/6$                     | 180                                           | D, J, P                   | Now          |

| PAL20   | 16R6                              | 20   | PAL16R6     | $t_{PD/S/CO} = 4.5/2.5/4.5, 5/2.5/5, 7/3.5/6$          | 180                                           | D, J, P                   | Now          |

| PAL20   | 16R4                              | 20   | PAL16R4     | $t_{PD/S/CO} = 4.5/2.5/4.5, 5/2.5/5, 7/3.5/6$          | 180                                           | D, J, P                   | Now          |

| PAL20   | 16L8                              | 20   | PALC16L8/L  | $t_{PD} = 20$                                          | 70,45                                         | D, L, P, Q, V, W          | Now          |

| PAL20   | 16R8                              | 20   | PALC16R8/L  | $t_{S/CO} = 15/12$                                     | 70,45                                         | D, L, P, Q, V, W          | Now          |

| PAL20   | 16R6                              | 20   | PALC16R6/L  | $t_{PD/S/CO} = 20/20/15$                               | 70,45                                         | D, L, P, Q, V, W          | Now          |

| PAL20   | 16R4                              | 20   | PALC16R4/L  | $t_{PD/S/CO} = 20/20/15$                               | 70,45                                         | D, L, P, Q, V, W          | Now          |

| PALCE20 | 16V8-Macrocell                    | 208  | PALCE16V8   | $t_{PD/S/CO} = 7.5/5/5, 10/6/7, 15/10/8$               | 115/90/55                                     | D, J, L, P                | Now          |

| PALCE24 | 20V8—Macrocell                    | 24   | PALCE20V8   | $t_{PD/S/CO} = 7.5/5/5, 10/6/7, 15/10/8$               | 115/90/55                                     | D, J, L, P                | Q494         |

| PAL24   | 22V10—Macrocell                   | 24S  | PALC22V10/L | $t_{PD/S/CO} = 25/15/15$                               | 90,55                                         | D, J, K, L, P, Q, W       | Now          |

| PAL24   | 22V10—Macrocell                   | 24S  | PALC22V10B  | $t_{PD/S/CO} = 15/10/10$                               | 90                                            | D, H, J, K, L,<br>P, Q, W | Now          |

| PAL24   | 22V10—Macrocell                   | 24S  | PAL22V10C   | t <sub>PD/S/CO</sub> = 6/3/5.5, 7.5/3/6,<br>10/3.6/7.5 | 190                                           | D, J, L, P                | Now          |

| PAL24   | 22VP10—Macrocell                  | 248  | PAL22VP10C  | $t_{PD/S/CO} = 6/3/5.5, 7.5/3/6, 10/3.6/7.5$           | 190                                           | D, J, L, P                | Now          |

| PALCE24 | 22V10-Macrocell                   | 24   | PALC22V10D  | $t_{PD/S/CO} = 7.5/5/5, 10/6/7, 15/10/8$               | 130/90/90                                     | D, J, L, P                | Now          |

| PAL24   | 22V10—Macrocell                   | 24   | PAL22V10G   | $t_{PD/S/CO} = 5/2.5/4, 6/3/5.5$                       | 190                                           | D, J, L                   | Now          |

| PAL24   | 22VP10—Macrocell                  | 24   | PAL22VP10G  | $t_{PD/S/CO} = 5/2.5/4, 6/3/5.5$                       | 190                                           | D,J,L                     | Now          |

| PLD24   | 20G10—Generic                     | 24S  | PLDC20G10   | $t_{PD/S/CO} = 25/15/15$                               | 55                                            | D, J, L, P, Q, W          | Now          |

| PLD24   | 20G10—Generic                     | 24S  | PLDC20G10B  | $t_{PD/S/CO} = 15/12/10$                               | 70                                            | D, H, J, L, P, Q, W       | Now          |

| PLD24   | 20G10—Generic                     | 24S  | PLD20G10C   | $t_{PD/S/CO} = 7.5/3/6.5, 10/3.6/7.5$                  | 190                                           | D, J, L, P                | Now          |

| PLD24   | 20RA10—Asynchronous               | 248  | PLD20RA10   | $t_{PD/S/CO} = 15/10/15$                               | 80                                            | D, H, J, L, P, Q, W       | Now          |

| PLD28   | 7C330—State Machine               | 28S  | CY7C330     | $f_{MAX.}$ , $t_{IS}$ , $t_{CO} = 66 MHz/3ns/12ns$     | 130@50<br>MHz                                 | D,H,J,L,P,Q,W             | Now          |

| PLD28   | 7C331—Asynchronous,<br>Registered | 28S  | CY7C331     | $t_{PD/S/CO} = 20/12/20$                               | 120@25 ns                                     | D, H, J, L, P, Q, W       | Now          |

| PLD28   | 7C335—Universal<br>Synchronous    | 28S  | CY7C335     | $f_{MAX}/t_{IS} = 100 \text{ MHz/2ns},$<br>83 MHz/2ns  | 140                                           | D,H,J,L,P,Q,W             | Now          |

### **CPLDs**

| Size             | Organization                      | Pins       | Part Number | Speed (ns)                                                        | I <sub>CC</sub> /I <sub>SB</sub> (mA) | Packages      | Availability |

|------------------|-----------------------------------|------------|-------------|-------------------------------------------------------------------|---------------------------------------|---------------|--------------|

| MAX28            | 7C344—32 Macrocell                | 28S        | CY7C344/B   | $t_{\text{PD/S/CO}} = 15/9/10, 10/6/5$                            | 200/150                               | D, H, J, P, W | Now          |

| MAX44            | 7C343—64 Macrocell                | 44         | CY7C343/B   | $t_{PD/S/CO} = 20/12/12, 12/8/6$                                  | 135/125                               | H, J, R       | Now          |

| MAX68            | 7C342—128 Macrocell               | 68         | CY7C342/B   | $t_{PD/S/CO} = 25/15/14, 12/8/6$                                  | 250/225                               | H, J, R       | Now          |

| MAX84            | 7C341—192 Macrocell               | 84         | CY7C341/B   | $t_{PD/S/CO} = 25/20/16, 15/10/7$                                 | 380/360                               | H, J, R       | Now          |

| MAX100           | 7C346—128 Macrocell               | 84,<br>100 | CY7C346/B   | $t_{PD/S/CO} = 25/15/14, 15/10/7$                                 | 250/225                               | H, J, N, R    | Now          |

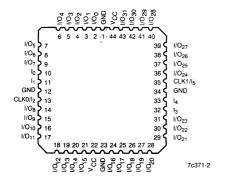

| Flash370-<br>44  | 7C371—32-Macrocell<br>Flash CPLD  | 44         | CY7C371     | $f_{MAX}/t_S/t_{CO} = 143MHz/6.5 \text{ ns/6.5 ns}$               | 150/TBD                               | J, Y          | Now          |

| Flash370-<br>44  | 7C372—64-Macrocell<br>Flash CPLD  | 44         | CY7C372     | $f_{MAX}/t_S/t_{CO} = 100 \text{ MHz/6.5 ns/6.5 ns}$              | 180/TBD                               | J, Y          | Q494         |

| Flash370-<br>84  | 7C373—64-Macrocell<br>Flash CPLD  | 84,<br>100 | CY7C373     | $f_{MAX}/t_S/t_{CO} = 100 \text{ MHz/6.5 ns/} $ 6.5 ns            | 180/TBD                               | A,J,G,Y       | Q494         |

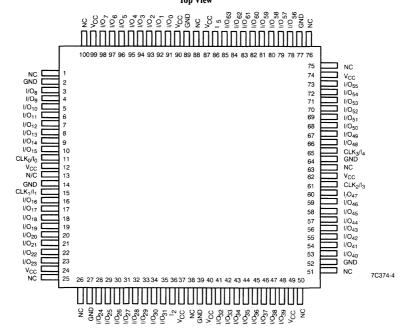

| Flash370-<br>84  | 7C374—128-Macrocell<br>Flash CPLD | 84,<br>100 | CY7C374     | $f_{MAX}/t_S/t_{CO} = 100 \text{ MHz/6.5 ns/} $ 6.5 ns            | 300/TBD                               | A, J, G, Y    | Now          |

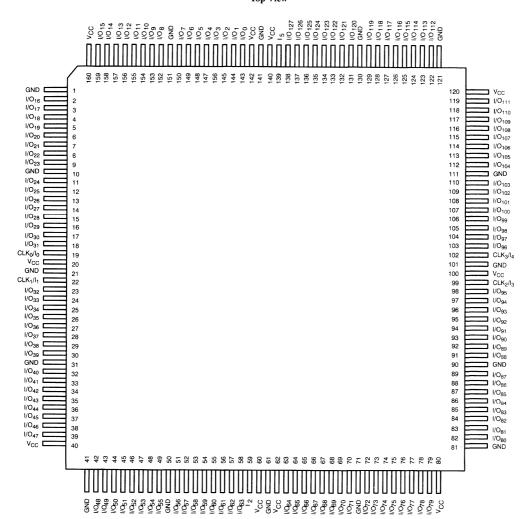

| Flash370-<br>160 | 7C375—128-Macrocell<br>Flash CPLD | 160        | CY7C375     | $f_{MAX}/t_{S}/t_{CO} = 100 \text{ MHz}/6.5 \text{ ns}/$ 6.5 ns   | 300/TBD                               | A,G,U         | Now          |

| Flash370-<br>160 | 7C376—192-Macrocell<br>Flash CPLD | 160        | CY7C376     | $f_{MAX}/t_S/t_{CO} = 83 \text{ MHz}/10 \text{ ns}/10 \text{ ns}$ | 300/TBD                               | A,G           | Q495         |

| Flash370-<br>240 | 7C377—192-Macrocell<br>Flash CPLD | 240        | CY7C377     | $f_{MAX}/t_S/t_{CO} = 83 \text{ MHz}/10 \text{ ns}/10 \text{ ns}$ | 300/TBD                               | BGA, N, G     | Q495         |

| FLASH370-<br>160 | 7C378—256-Macrocell<br>Flash CPLD | 160        | CY7C378     | $f_{MAX}/t_S/t_{CO} = 83 \text{ MHz}/10 \text{ ns}/10 \text{ ns}$ | 300/TBD                               | A,G           | Q295         |

| FLASH370-<br>240 | 7C379—256-Macrocell<br>Flash CPLD | 240        | CY7C379     | $f_{MAX}/t_S/t_{CO} = 83 \text{ MHz}/10 \text{ ns}/10 \text{ ns}$ | 300/TBD                               | BGA, N, G     | Q295         |

#### **FPGAs**

| Size                | Organization                     | Pins       | Part Number | Speed Grade | I <sub>CC</sub> /I <sub>SB</sub> (mA) | Packages | Availability |

|---------------------|----------------------------------|------------|-------------|-------------|---------------------------------------|----------|--------------|

| pASIC380-<br>1K     | CMOS 8x12, 1K Gates<br>FPGA      | 44         | CY7C381A    | -0, -1, -2  | $I_{SB} = 10$                         | J        | Now          |

| pASIC380-<br>1K     | CMOS 8x12, 1K Gates<br>FPGA      | 68,<br>100 | CY7C382A    | -0, -1, -2  | $I_{SB} = 10$                         | A,G,J    | Now          |

| pASIC380-<br>1K3.3V | 3.3V CMOS 8x12, 1K<br>Gates FPGA | 44         | CY7C3381A   | -0, -1, -2  | $I_{SB} = 2$                          | J        | Q394         |

| pASIC380-<br>1K3.3V | 3.3V CMOS 8x12, 1K<br>Gates FPGA | 68,<br>100 | CY7C3382A   | -0, -1, -2  | $I_{SB} = 2$                          | A, G, J  | Q394         |

| pASIC380-<br>2K     | CMOS 12x16, 2K Gates<br>FPGA     | 68         | CY7C383A    | -0, -1, -2  | $I_{SB} = 10$                         | J        | Now          |

| pASIC380-<br>2K     | CMOS 12x16, 2K Gates<br>FPGA     | 84,<br>100 | CY7C384A    | -0, -1, -2  | $I_{SB} = 10$                         | A, G, J  | Now          |

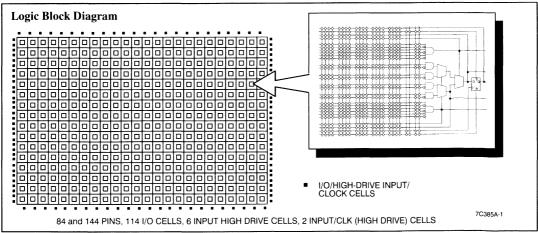

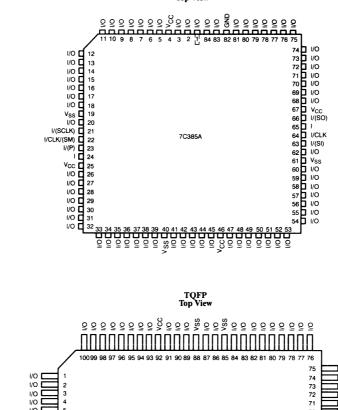

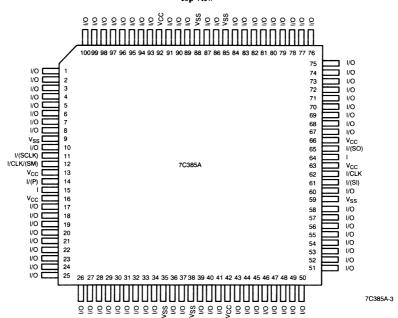

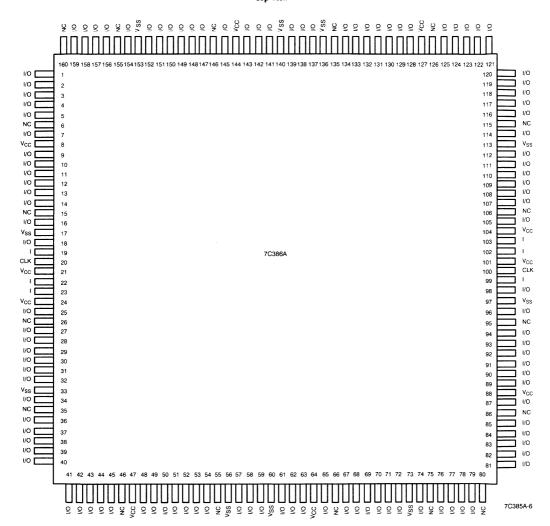

| pASIC380-<br>4K     | CMOS 16x24, 4K Gates<br>FPGA     | 84,<br>100 | CY7C385A    | -0, -1, -2  | $I_{SB} = 10$                         | A,J      | Now          |

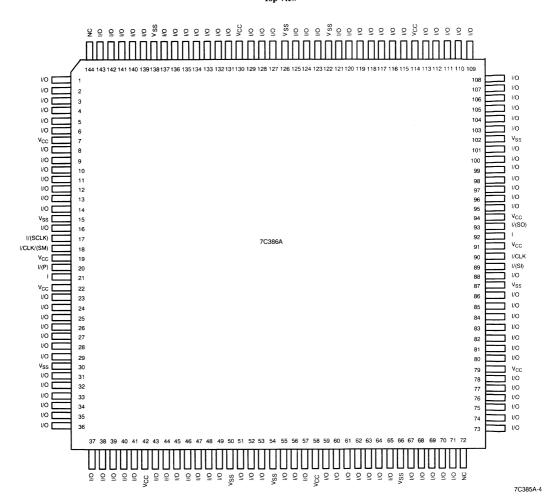

| pASIC380-<br>4K     | CMOS 16x24, 4K Gates<br>FPGA     | 144<br>160 | CY7C386A    | -0, -1, -2  | $I_{SB} = 10$                         | A,G,U    | Now          |

| pASIC380-<br>8K     | CMOS 24x32, 8K Gates<br>FPGA     | 144        | CY7C387A    | -0, -1, -2  | $I_{SB} = 10$                         | A,G      | Q195         |

| pASIC380-<br>8K     | CMOS 24x32, 8K Gates<br>FPGA     | 208        | CY7C388A    | -0, -1, -2  | $I_{SB} = 10$                         | N, G     | Q195         |

| pASIC380-<br>12K    | CMOS 32x36, 12K Gates<br>FPGA    | 208        | CY7C389A    | -0, -1, -2  | $I_{SB} = 10$                         | N        | Q495         |

#### **Design and Programming Tools**

| Part Name     | Туре                 | Part Number |

|---------------|----------------------|-------------|

| Warp2 for PC  | VHDL Design Tool     | CY3120      |

| Warp2 for Sun | VHDL Design Tool     | CY3125      |

| Warp3 for PC  | VHDL/CAE Design Tool | CY3130      |

| Warp3 for Sun | VHDL/CAE Design Tool | CY3135      |

| Impulse3      | Programmer           | CY3500      |

#### Notes

The above specifications are for the commercial temperature range of  $0^{\circ}$ C to  $70^{\circ}$ C. Military temperature range  $(-55^{\circ}$ C to  $+125^{\circ}$ C) product processed to MIL-STD-883 Revision C is also available for most products. Speed and power selections may vary from those above. Contact your local sales office for more information.

Commercial grade product is available in plastic, CERDIP, or LCC. Military grade product is available in CERDIP, LCC, or PGA. F, K, and T packages are special order only.

All power supplies are  $V_{CC} = 5V \pm 10\%$ .

22S, 24S, 28S stands for 300 mil. 22-pin, 24-pin, 28-pin, respectively. 28.4 stands for 28-pin 400 mil, 24.4 stands for 24-pin 400 mil.

PLCC, SOJ, and SOIC packages are available on some products.

F, K, and T packages are special order only.

#### Package Code:

B = PLASTIC PIN GRID ARRAY S = SOICT = WINDOWED CERPACK D = CERDIPE = TAPE AUTOMATED BOND U = CERAMIC QUAD FLATPACK V = SOJ(TAB) F = FLATPACKW = WINDOWED CERDIP G = PIN GRID ARRAY (PGA)X = DICEY = CERAMIC LCC H = WINDOWED HERMETIC LCC J = PLCCZ = TSOPHD = HERMETIC DIP (Module) K = CERPACKL = LEADLESS CHIP CARRIER (LCC) HV = HERMETIC VERTICAL DIP PF = PLASTIC FLAT SIP N = PLASTIC QUAD FLATPACK P = PLASTICPS = PLASTIC SIP

P = PLASTIC PS = PLASTIC SIP

Q = WINDOWED LCC PZ = PLASTIC ZIP

R = WINDOWED PGA BG = BALL GRID ARRAY

| CYPRESS        | CYPRESS        | ALTERA    | CYPRESS      | AMD             | CYPRESS                 |

|----------------|----------------|-----------|--------------|-----------------|-------------------------|

| PALC16L8-25C   | PALC16L8L-25C  | 5064JM    | 7C343-35HMB  | SMDPN           | SMDPN                   |

| PALC16L8-30M   | PALC16L8-20M   | 5064LC    | 7C343-35JC   | 5962-8515501RX  | 5962-88713 09RX         |

| PALC16L8-35C   | PALC16L8-25C   | 5064LC-1  | 7C343-25JC   | 5962-85155 012X | 5962-88713 09XX         |

| PALC16L8-40M   | PALC16L8-30M   | 5064LC-2  | 7C343-30JC   | 5962-85155 02RX | 5962-88713 10RX         |

| PALC16L8L-35C  | PALC16L8L-25C  | 5128AGC-1 | 7C342B-12RC  | 5962-85155 022X | 5962-88713 10XX         |

| PALC16R4-25C   | PALC16R4L-25C  | 5128AGC-2 | 7C342B-15RC  | 5962-85155 03RX | 5962-88713 11RX         |

| PALC16R4-30M   | PALC16R4-20M   | 5128AGC-3 | 7C342B-20RC  | 5962-85155 032X | 5962-8871311XX          |

| PALC16R4-35C   | PALC16R4-25C   | 5128AJC-1 | 7C342B-12HC  | 5962-85155 04RX | 5962-88713 12RX         |

| PALC16R4-40M   | PALC16R4-30M   | 5128AJC-2 | 7C342B-15HC  | 5962-85155 042X | 5962-88713 12XX         |

| PALC16R4L-35C  | PALC16R4L-25C  | 5128AJC-3 | 7C342B-20HC  | 5962-85155 05RX | 5962-88713 09RX         |

| PALC16R6-25C   | PALC16R6L-25C  | 5128ALC-1 | 7C342B-12JC  | 5962-85155 052X | 5962-88713 09XX         |

| PALC16R6-30M   | PALC16R6-20M   | 5128ALC-2 | 7C342B-15JC  | 5962-85155 06RX | 5962-88713 10RX         |

| PALC16R6-35C   | PALC16R6-25C   | 5128ALC-3 | 7C342B-20JC  | 5962-85155 062X | 5962-88713 10XX         |

| PALC16R6-40M   | PALC16R6-30M   | 5128GC    | 7C342-35RC   | 5962-85155 07RX | 5962-88713 11RX         |

| PALC16R6L-35C  | PALC16R6L-25C  | 5128GC-1  | 7C342-25RC   | 5962-85155 072X | 5962-8871311XX          |

| PALC16R8-25C   | PALC16R8L-25C  | 5128GC-2  | 7C342-30RC   | 5962-85155 08RX | 5962-88713 12RX         |

| PALC16R8-30M   | PALC16R8-20M   | 5128GM    | 7C342-35RMB  | 5962-85155 082X | 5962-88713 12XX         |

| PALC16R8-35C   | PALC16R8-25C   | 5128JC    | 7C342-35HC   | 5962-85155 09RX | 5962-9233801MRX         |

| PALC16R8-40M   | PALC16R8-30M   | 5128JC-1  | 7C342-25HC   | 5962-85155 092X | 5962-92338 01MXX        |

| PALC16R8L-35C  | PALC16R8L-25C  | 5128JC-2  | 7C342-30HC   | 5962-85155 10RX | 5962-92338 01MRX        |

| PALC22V10-35C  | PALC22V10-25C  | 5128JI    | 7C342-35HI   | 5962-85155 102X | 5962-92338 02MXX        |

| PALC22V10-40M  | PALC22V10-30M  | 5128JI-2  | 7C342-30HI   | 5962-85155 11RX | 5962-92338 03MRX        |

| PALC22V10L-25C | PALC22V10-25C  | 5128JM    | 7C342-35HMB  | 5962-85155 112X | 5962-92338 03MXX        |

| PALC22V10L-35C | PALC22V10L-25C | 5128LC    | 7C342-35JC   | 5962-85155 12RX | 5962-92338 04MRX        |

| PLDC20G10-35C  | PLDC20G10-25C  | 5128LC-1  | 7C342-25JC   | 5962-85155 122X | 5962-92338 04MXX        |

| PLDC20G10-40M  | PLDC20G10-30M  | 5128LC-2  | 7C342-30JC   | 5962-85155 13RX | 5962-92338 01MRX        |

|                |                | 5128LI    | 7C342-35JI   | 5962-85155 14RX | 5962-92338 02MRX        |

| ALTERA         | CYPRESS        | 5128LI-2  | 7C342-30HI   | 5962-85155 15RX | 5962-92338 03MRX        |

| PREFIX:EPM     | PREFIX:CY      | 5130GC    | 7C346-35RC   | 5962-85155 16RX | 5962-92338 04MRX        |

| 5032DC         | 7C344-25WC     | 5130GC-1  | 7C346-25RC   | 5962-85155 17RX | 5962-9233801MRX         |

| 5032DC-2       | 7C344-20WC     | 5130GC-2  | 7C346-30RC   | 5962-85155 18RX | 5962-92338 02MRX        |

| 5032DC-15      | 7C344-15WC     | 5130GM    | 7C346-35RM   | 5962-85155 19RX | 5962-92338 03MRX        |

| 5032DC-17      | Call Factory   | 5130JC    | 7C346-35HC   | 5962-85155 20RX | 5962-92338 04MRX        |

| 5032DC-20      | 7C344-20WC     | 5130JC-1  | 7C346-25HC   | 5962-86053 01LA | 5962-89841 01LX         |

| 5032DC-25      | 7C344-25WC     | 5130JC-2  | 7C346-30HC   | 5962-86053 013A | 5962-89841 013X         |

| 5032DM         | 7C344-25WMB    | 5130JM    | 7C346-35HM   | 5962-86053 01KA | 5962-89841 01 <b>KX</b> |

| 5032DM-25      | 7C344-25WMB    | 5130LC    | 7C346-35JC   | 5962-86053 02LA | 5962-89841 01LX         |

| 5032JC         | 7C344-25HC     | 5130LC-1  | 7C346-25JC   | 5962-86053 023A | 5962-89841 013X         |

| 5032JC-2       | 7C344-20HC     | 5130LC-2  | 7C346-30JC   | 5962-86053 02KA | 5962-89841 01KX         |

| 5032JC-15      | 7C344-15HC     | 5130LI    | 7C346-35JI   | 5962-86053 04LA | 5962-89841 02LX         |

| 5032JC-17      | Call Factory   | 5130LI-2  | 7C346-30JI   | 5962-86053 043A | 5962-89841 023X         |

| 5032JC-20      | 7C344-20HC     | 5130QC    | 7C346-35NC   | 5962-86053 04KA | 5962-89841 02KX         |

| 5032JC-25      | 7C344-25HC     | 5130QC-1  | 7C346-25NC   | 5962-86053 053A | 5962-89841 063X         |

| 5032J1-20      | 7C344-20HI     | 5130QC-2  | 7C346-30NC   | 5962-86053 05KA | 5962-89841 06KX         |

| 5032JM         | 7C344-25HMB    | 5130QI    | 7C346-35NI   | 5962-86053 05LA | 5962-89841 06LX         |

| 5032JM-25      | 7C344-25HMB    | 5192AGC-1 | 7C341B-15RC  | 5962-8851501RX  | 5962-88713 09RX         |

| 5032LC         | 7C344-25JC     | 5192AGC-2 | 7C341B-20RC  | 5962-88515 012X | 5962-88713 09XX         |

| 5032LC-2       | 7C344-20JC     | 5192AJC-1 | 7C341B-15HC  | 5962-88515 02RX | 5962-88713 10RX         |

| 5032LC-15      | 7C344-15JC     | 5192AJC-2 | 7C341B-20HC  | 5962-88515 022X | 5962-88713 10XX         |

| 5032LC-17      | Call Factory   | 5192ALC-1 | 7C341B-15JC  | 5962-88515 03RX | 5962-8871311RX          |

| 5032LC-20      | 7C344-20JC     | 5192ALC-2 | 7C431B-20JC  | 5962-88515 032X | 5962-8871311XX          |

| 5032LC-25      | 7C344-25JC     | 5192GC    | 7C341-35RC   | 5962-88515 04RX | 5962-88713 12RX         |

| 5032PC         | 7C344-25PC     | 5192GC-1  | 7C341 – 25RC | 5962-88515 042X | 5962-88713 12XX         |

| 5032PC-2       | 7C344-20PC     | 5192GC-2  | 7C341 – 30RC | PREFIX:Am       | PREFIX:CY               |

| 5032PC-15      | 7C344-15PC     | 5192JC    | 7C341 – 35HC | PREFIX:SN       | PREFIX:CY               |

| 5032PC-17      | Call Factory   | 5192JC-1  | 7C341 –25HC  | SUFFIX:B        | SUFFIX:B                |

| 5032PC-20      | 7C344-20PC     | 5192JC-2  | 7C341 – 30HC | SUFFIX:D        | SUFFIX:DORW             |

| 5032PC-25      | 7C344-25PC     | 5192JI    | 7C341 – 35HI | SUFFIX:F        | SUFFIX:F                |

| 5064JC         | 7C343-35HC     | 5192LC    | 7C341 – 35JC | SUFFIX:L        | SUFFIX:L                |

| 5064JC-1       | 7C343-25HC     | 5192LC-1  | 7C341 - 25JC | SUFFIX:P        | SUFFIX:P                |

| 5064JC-2       | 7C343 – 30HC   | 5192LC-2  | 7C341-30JC   | MACH110-12JC    | 7C371 –83JC             |

| 5064JI         | 7C343-35HI     | L         |              | MACH110-15JC    | 7C371-66JC              |

### **Product Line Cross Reference**

| AMD                        | CYPRESS                       | AMD                                | CYPRESS                             | AMD                    | CYPRESS                       |

|----------------------------|-------------------------------|------------------------------------|-------------------------------------|------------------------|-------------------------------|

| MACH110-20JC               | 7C371-66JC                    | PAL16R6ALM                         | PALC16R6-30M                        | PALCE22V10H-7JC        | PALC22V10D-10JC               |

| MACH110 - 20/BXA           | 7C371 - 66YMB                 | PAL16R6AM                          | PALC16R6-30M                        | PALCE22V10H-10PC       | PALC22V10D-103C               |

| MACH130-15JC               | 7C373 – 83JC                  | PAL16R6BM                          | PALC16R6-20M                        | PALCE22V10H-10JC       | PALC22V10D-10JC               |

| MACH130-20JC               | 7C373-66JC                    | PAL16R6C                           | PALC16R6-35C                        | PALCE22V10H-10PC       | PALC22V10D-10PC               |

| MACH130-20/BXA             | 7C373-66YMB                   | PAL16R6LC                          | PALC16R6-35C                        | PALCE22V10H            | PALC22V10D                    |

| MACH210-12JC               | 7C372-100JC                   | PAL16R6LM                          | PALC16R6-40M                        | -15/B3A                | -15LMB                        |

| MACH210-15JC               | 7C372-83JC                    | PAL16R6M                           | PALC16R6-40M                        | PALCE22V10H            | PALC22V10D                    |

| MACH210-20JC               | 7C372-66JC                    | PAL16R6QC                          | PALC16R6L-35C                       | -15/BLA                | -15DMB                        |

| MACH210-20/BXA             | 7C372-66YMB                   | PAL16R6QM                          | PALC16R6-40M                        | PALCE22V10H-15JC       | PALC22V10D-15JC               |

| MACH210A-10JC              | 7C372-125JC                   | PAL16R8-4C                         | PAL16R8-4C                          | PALCE22V10H-15PC       | PALC22V10D-15PC               |

| MACH210A-12JC              | 7C372-100JC                   | PAL16R8-5C                         | PAL16R8-5C                          | PALCE22V10H<br>-20/B3A | PALC22V10D<br>-20LMB          |

| MACH230-15JC               | 7C374-83JC                    | PAL16R8-7C                         | PAL16R8-7C                          | PALCE22V10H            | PALC22V10D                    |

| MACH230-20JC               | 7C374-66JC                    | PAL16R8-10/B                       | PAL16R8-10M                         | -20/BLA                | -20DMB                        |

| MACH435-15JC               | 7C374-83JC<br>7C374-66JC      | PAL16R8-12/B<br>PAL16R8-D/2        | PAL16R8-10M                         | PALCE22V10H            | PALC22V10D                    |

| MACH435-20JC<br>PAL16L8-4C | PAL16L8-4C                    | PAL16R8A-4C                        | PAL16R8-7C<br>PALC16R8L-35          | -25/B3A                | -25LMB                        |

| PAL16L8-4C                 | PAL16L8-5C                    | PAL16R8A-4M                        | PALC16R8-40M                        | PALCE22V10H            | PALC22V10D                    |

| PAL16L8-7C                 | PAL16L8-7C                    | PAL16R8AC                          | PALC16R8-25C                        | -25/BLA                | -25DMB                        |

| PAL16L8-10/B               | PAL16L8-10M                   | PAL16R8ALC                         | PALC16R8-25C                        | PALCE22V10H-25JC       | PALC22V10D-25JC               |

| PAL16L8-12/B               | PAL16L8-10M                   | PAL16R8ALM                         | PALC16R8-30M                        | PALCE22V10H-25PC       | PALC22V10D-25PC               |

| PAL16L8-D/2                | PAL16L8-7C                    | PAL16R8AM                          | PALC16R8-30M                        | PALCE22V10H<br>-30/B3A | PALC22V10D<br>-25LMB          |

| PAL16L8A-4C                | PALC16L8L-35C                 | PAL16R8BM                          | PALC16R8-20M                        | PALCE22V10H            | PALC22V10D                    |

| PAL16L8A-4M                | PALC16L8-40M                  | PAL16R8C                           | PALC16R8-35C                        | -30/BLA                | -25DMB                        |

| PAL16L8AC                  | PALC16L8-25C                  | PAL16R8LC                          | PALC16R8-35C                        |                        | 202111                        |

| PAL16L8ALC                 | PALC16L8-25C                  | PAL16R8LM                          | PALC16R8-40M                        | ATMEL                  | CYPRESS                       |

| PAL16L8ALM                 | PALC16L8-30M                  | PAL16R8M                           | PALC16R8-40M                        | PREFIX:AT              | PREFIX:CY                     |

| PAL16L8AM                  | PALC16L8-30M                  | PAL16R8QC                          | PALC16R8L-35                        | 22V10                  | PALC22V10                     |

| PAL16L8BM                  | PALC16L8-20M                  | PAL16R8QM                          | PALC16R8-40M                        | 22V10-15               | PALC22V10B                    |

| PAL16L8C                   | PALC16L8-35C                  | PAL22V10-7JC                       | PALC22V10D-7JC                      | HARRIS                 | CYPRESS                       |

| PAL16L8LC                  | PALC16L8-35C                  | PAL22V10-7PC                       | PALC22V10D-7PC                      | PREFIX:HM              | PREFIX:CY                     |

| PAL16L8LM                  | PALC16L8-40M                  | PAL22V10-10DC                      | PALC22V10D-10DC                     | PREFIX:HPL             | PREFIX:CY                     |

| PAL16L8M                   | PALC16L8-40M                  | PAL22V10-10JC                      | PALC22V10D-10JC                     | SUFFIX:8               | SUFFIX:B                      |

| PAL16L8QC<br>PAL16L8QM     | PALC16L8L-35C<br>PALC16L8-40M | PAL22V10-10PC<br>PAL22V10-12/B3A   | PALC22V10D-10PC<br>PALC22V10B-10LMB | PREFIX:1               | SUFFIX:D                      |

| PAL16R4-4C                 | PAL16R4-4C                    | PAL22V10-12/BJA<br>PAL22V10-12/BLA | PALC22V10B-10DMB                    | PREFIX:9               | SUFFIX:F                      |

| PAL16R4-5C                 | PAL16R4-5C                    | PAL22V10-15DC                      | PALC22V10B-15DC                     | PREFIX:4               | SUFFIX:L                      |

| PAL16R4-7C                 | PAL16R4-7C                    | PAL22V10-15JC                      | PALC22V10B-15JC                     | PREFIX:3               | SUFFIX:P                      |

| PAL16R4-10/B               | PAL16R4-10M                   | PAL22V10-15PC                      | PALC22V10B-15PC                     | 16LC8-5                | PALC16L8L-35C                 |

| PAL16R4-12/B               | PAL16R4-10M                   | PAL22V10-20/B3A                    | PALC22V10B-20LMB                    | 16LC8-8                | PALC16L8-40M                  |

| PAL16R4-D/2                | PAL16R4-7C                    | PAL22V10-20/BLA                    | PALC22V10B-20DMB                    | 16LC8-9<br>16RC4-5     | PALC16L8-40M<br>PALC16R4L-35C |

| PAL16R4A-4C                | PALC16R4L-35C                 | PAL22V10/B3A                       | PALC22V10-35LMB                     | 16RC4-8                | PALC16R4L-33C<br>PALC16R4-40M |

| PAL16R4A-4M                | PALC16R4-40M                  | PAL22V10/BLA                       | PALC22V10-35DMB                     | 16RC4-9                | PALC16R4-40M                  |